## **Multi-Domain Fault Simulation Using Virtual Prototypes**

#### Dissertation

der Mathematisch-Naturwissenschaftlichen Fakultät

der Eberhard Karls Universität Tübingen

zur Erlangung des Grades eines

Doktors der Naturwissenschaften

(Dr. rer. nat.)

vorgelegt von

M.Sc. Raghavendra Koppak

aus Sri Ramnagar, Karnataka, India

Tübingen

2021

| Gedruckt mit Genehmigung der<br>Eberhard Karls Universität Tübingen. | Mathematisch-Naturwissenschaftlichen Fakultät der    |

|----------------------------------------------------------------------|------------------------------------------------------|

| Tag der mündlichen Qualifikation: Dekan:  1. Berichterstatter:       | 19.07.2022 Prof. Dr. Oliver Bringmann                |

| <ul><li>1. Berichterstatter:</li><li>2. Berichterstatter:</li></ul>  | Prof. Dr. Oliver Bringmann Prof. Dr. Joachim Gerlach |

|                                                                      |                                                      |

# **DECLARATION**

I hereby declare that I alone wrote the doctoral work submitted here under the title "Multi-Domain Fault Simulation Using Virtual Prototypes", that I only used the sources and materials cited in the work, and that all citations, whether word for word or paraphrased are given as such.

Raghavendra Koppak

Tübingen, 21.12.2021

| "A goal is a dream with a deadline."  - Napoleon hill                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Treat failure as a lesson on how not to approach achieving a goal, and then use that learning to improve your chances of success when you try again. Failure is only the end if you decide to stop."  - Richard Branson |

| "Education is the most powerful weapon which you can use to change the world."  - Nelson Mandela                                                                                                                         |

|                                                                                                                                                                                                                          |

# Kurzfassung

Industrielle elektronische Systeme, die die Fertigungsprozesse sowie die Bewegungsteuerung der Fertigungsmaschinen in modernen, hochautomatisierten Produktionsanlagen steuern, sind hochkomplex geworden und kombinieren eine Vielzahl von elektronischen, elektrischen und mechanischen Komponenten, die während ihres Betriebs reibungslos zusammenwirken müssen. Die hohen Anforderungen bei der Entwicklung zukünftiger Produktionsanlagen werden insbesondere an sogenannte Motion-Control-Systeme gestellt, die beispielsweise die schnelle und präzise Positionierung und Bewegungssteuerung von Förderbändern und Roboterarmen übernehmen. Diese Systeme müssen Störungen aller Art bewältigen und die Sicherheit des Bedienpersonals und die Integrität der Maschine jederzeit gewährleisten. Aber was passiert, wenn z.B. einzelne Chips in der Steuerung eines Roboters ausfallen, ein Motor aufgrund eines Lagerschadens überhitzt oder ein Sensor fehlerhafte Daten liefert? Ist es möglich, die Steuerungssoftware dieser Systeme so zu entwickeln und zu testen, dass bei Störungen an einer oder mehreren Komponenten das Gesamtsystem immer in einem sicheren Zustand verbleibt? Ist es ferner gewährleistet, dass Menschen in der Nähe dieser Maschinen nicht geschädigt und teure Komponenten, wie Motoren oder Roboterarme, nicht zerstört werden? Bis heute basieren die Endtests dieser Systeme hauptsächlich auf realen Prototypen, um den korrekten und sicheren Betrieb zu sicherzustellen.

In der konventionellen Systementwicklung sind daher reale Prototypen und umfangreiche Systemtests notwendig. Diese Prototypen sind jedoch erst in späteren Phasen des Entwurfsprozesses verfügbar. Diese Tests sind bereits heute aufwendig und teuer und sind nicht in der Lage alle möglichen Fehlerarten vollständig abdecken, da bestimmte Fehler in der realen Hardware nicht provoziert werden können. Außerdem kann die späte Ausführung der Tests zu langen Iterationsschleifen führen, falls bei den abschließenden Tests Schwachstellen festgestellt werden. Noch anspruchsvoller wird die Validierung für die hochflexiblen, selbstkonfigurierenden, selbstheilenden Steuerungssysteme zukünftiger Fertigungsszenarien mit Fokus auf die Automatisierung kleiner Losgrößen, die eine wesentlich höhere Konfigurierbarkeit der Systeme und eine engere Interaktion zwischen Mensch und Maschine erfordern.

Die Fehlerinjektion in Low-Level-Simulationsmodelle ist weit verbreitet, um einen sicheren Betrieb unter unerwarteten Bedingungen, wie z.B. Eigenausfällen der Elektronik

oder umweltbedingten Ausfällen, zu validieren. Für eine schnelle Simulation der Systeme ist jedoch eine hohe Abstraktion der Modelle erforderlich und die Fehlersimulation bietet einen Kompromiss zwischen Genauigkeit und Simulationsleistung. Virtuelle Prototypen (VPs) ermöglichen es, Systemtests in einem frühen Entwicklungsstadium durchzuführen. Aber sie leiden immer noch unter einer unzureichenden Werkzeugunterstützung und Methodik. VPs haben z.B. keine Simulator Unterstützung mit inhärenten Fehlerinjektionstechniken. Darüber hinaus nutzen Ingenieurgruppen aus verschiedenen Bereichen verschiedene Modellierungssprachen und -Werkzeuge, um Modelle zu entwickeln und ihre Entwürfe in der Industrie zu bewerten.

In dieser Arbeit wird eine kombinierte Technik zur Modellierung von Fehlern in Multi-Domain-Systemen vorgeschlagen, die eine frühzeitige Validierung dieser heterogenen Systeme ermöglicht. Die Validierung erfolgt mittels virtueller Stresstests durch Zusammenführung verschiedener Domänen in eine Simulationsplattform. Es werden geeignete Techniken beschrieben, um physikalische Komponentenmodelle so zu erweitern oder zu entwickeln, dass sie Fehlerinjektionsmöglichkeiten beinhalten, bevor sie in eine virtuelle Plattform importiert werden. Dabei werden nur physikalische Komponentenmodelle berücksichtigt, die mit MATLAB/Simulink modelliert werden, da nicht-digitale Teile des Systems in der Industrie häufig mit MATLAB/Simulink modelliert werden. In dieser Dissertation wird die im Rahmen des EffektiV-Projekts entwickelte TLM-basierte Fehlerinjektionsinfrastruktur genutzt, um durch die Entwicklung geeigneter Fehlermodelle Fehler in digitale Bauteile zu injizieren. Darüber hinaus wird ein generisches Fehlerinjektions-Framework vorgeschlagen und implementiert, ıım Fehlerinjektionsexperimente auf der Basis virtueller Prototypen durchzuführen. Mit diesem Framework werden die Fehler in die heterogenen Komponenten der industriellen Systeme (Motion Control Systeme) entweder interaktiv während der Simulationslaufzeit aktiviert oder als Regressionstests mit Hilfe von Skripten ausgeführt. Des Weiteren werden Nachbearbeitungstechniken vorgeschlagen, um die Ergebnisse der Regressionstests automatisch auszuwerten. Ferner werden die vorvalidierten Fehlermodelle in ein Hardwarein-the-Loop (HiL)Testsystem bei Siemens integriert, wodurch eine abschließende Validierung der Fehlersicherheit der Systeme vor der Produktfreigabe ermöglicht wird.

Die vorgeschlagenen Methoden werden am Beispiel einer industriellen Motorsteuerung mit zwei virtuellen HiL- und einem HiL-Demonstrator evaluiert: (i)

Industrielle Motorsteuerung mit Motorsignalaufbereitung mittels Beschleunigungssensor. (ii) Industrielle Motorsteuerung und Förderbandanwendung basierend auf dem V-REP (Virtual Robotic Experimentation Platform) Simulator. (iii) HIL-Testsystem basierend auf einem Siemens SINAMICS G120 Antrieb. Es konnte gezeigt werden, dass die Ergebnisse dieser Arbeit zu einer Anpassung der zukünftigen Produktentwicklung für industrielle elektronische Systeme bei der Siemens AG führen kann.

*Schlüsselwörter*: Industrie 4.0, Cyber Physical Systems, Virtueller Prototyp, Fehlersimulation, Hardware-in-the-Loop (HIL), Virtuelle Hardware-in-the-Loop (vHIL), Physische Komponentenmodelle, Fehlerübertragung, SystemC/TLM, Multi-Domain Simulation, MATLAB/Simulink, Simscape, Validierung.

## **ABSTRACT**

Industrial electronic systems that control manufacturing and machine motion in modern, highly automated production facilities have become highly complex, which combine a variety of electronic, electrical, and mechanical components that need to interact smoothly during their operation. The high critical issues in the development of future production plants are imposed by motion control systems, which manage the fast and most accurate positioning and motion control of conveyor belts and robot arms, for instance. These systems are required to properly cope with failures of all kinds to guarantee safety of operators and machine integrity at any time. But what happens, if for instance single chips in a robot's control unit fail, if a motor due to a bearing damage overheats or a sensor delivers faulty data? Is it possible to develop and test the control software of these systems in a way that in case of faults in one or more components the total system always remains in a safe state? Is it guaranteed that humans near to these machines are not harmed and expensive parts like motors or robot arms are not destroyed? As of today, the final tests of those systems are mainly based on physical prototypes to ensure the correct and safe operation.

In conventional system development, physical prototypes and extensive system tests are needed. However, those prototypes are available only in later phases of the design process. These tests are complex and expensive already today and are not able to completely cover all possible kinds of failures, as certain failures cannot be provoked in real hardware. Moreover, the late execution of the tests may cause long iteration loops in case weaknesses are detected in the final tests. The validation becomes even more challenging for the highly flexible, self-configuring, self-healing control systems of future manufacturing scenarios with focus on automation of small lot sizes, which requires much higher configurability of the systems and closer interaction between humans and manufacturing machines.

Fault injection into low level simulation models is widely used for validating the satisfactory operation under unexpected conditions like intrinsic failures of electronics or failures caused by the environment. However, a high level of abstraction of models is required for fast simulation of the systems and fault simulation is a trade-off between accuracy and simulation performance. Virtual prototypes (VPs) provide a possibility to perform system tests in an early stage of development. But they still suffer from less tool support and methodology features e.g. VPs lack simulator support with inherent fault-injection features.

Additionally, engineering groups of different domains exploit different modeling languages and tools to develop models and evaluate their designs in industry.

In this work, combined techniques to model faults in multi-domain systems are proposed which make early validation of these heterogeneous systems possible. The validation is performed by conducting virtual stress tests after bringing together different domains into one simulation platform. Suitable techniques are described, to enhance or develop physical component models such that they incorporate fault injection possibilities before being imported into a virtual platform. Only physical components models that are modeled using MATLAB/Simulink are considered, as non-digital parts of the system are often modeled in industry using MATLAB/Simulink. The TLM-based fault injection infrastructure developed under the EffektiV project is used to inject faults in digital parts by developing appropriate fault models. Furthermore, a generic fault injection framework is proposed and implemented to conduct fault injection experiments based on virtual prototypes. Using this framework, the faults in heterogeneous parts of the industrial systems (motion control systems) are either activated interactively during simulation runtime or executed as regression tests using scripts. Also, the post processing techniques are proposed to automatically evaluate the results of regression tests. Later, these pre-validated fault models are integrated in a hardware-in-the-loop (HIL) test system at Siemens, which enables a final validation of the systems' safety against faults before product release.

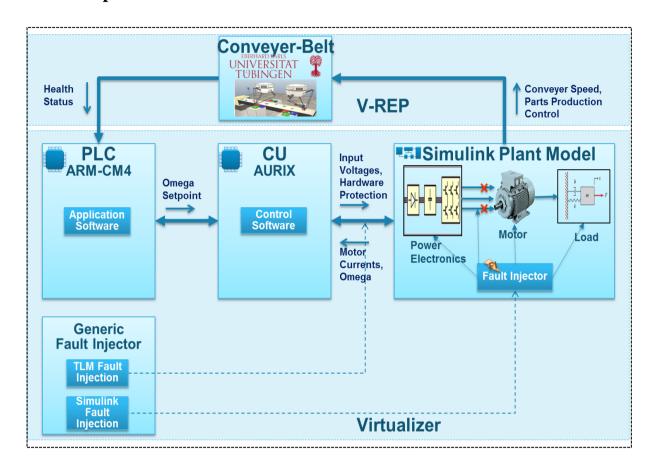

The proposed methodologies are evaluated using an industrial motor control application example with two virtual HIL and one HIL demonstrators: (i) Industrial motor control system with motor signal conditioning using acceleration sensor. (ii) Industrial motor control system along with conveyor-belt application based on the V-REP (Virtual Robotic Experimentation Platform) simulator. (iii) HIL test system based on a Siemens SINAMICS G120 drive. It has been shown that the contributions from this study provided further directions in future product development for industrial electronic systems at Siemens AG.

*Keywords*: Industrial 4.0, Cyber Physical Systems, Virtual Prototype, Fault Simulation, Hardware-in-the-loop (HIL), Virtual Hardware-In-the-Loop (vHIL), Physical Component Models, Fault Transfer, SystemC/TLM, Multi-Domain Simulation, MATLAB/Simulink, Simscape, Validation.

# **PREFACE**

This dissertation has been submitted to the Eberhard-Karls-University of Tuebingen in partial fulfilment of the requirements for the doctoral degree at computer science department (Wilhelm-Schickard-Institute for Computer Science). The work has been carried out at the DF TI AT (Advanced Technologies) department, Siemens AG Nuremberg under the supervision of Prof. Dr. Oliver Bringmann, Prof. Dr. Joachim Gerlach (Department of Computer science, Albstadt-Sigmaringen University) and Dr. Andreas von Schwerin.

## **ACKNOWLEDEGEMENT**

I would like to take this opportunity to remember all those who gave me the possibility to develop, to learn, to know myself better and finally to make life a memorable and unforgettable experience during this PhD thesis and beyond.

I express my gratitude to my colleagues at Siemens AG in the Department of DI, AT, ATS who supported me in my research work and maintained a pleasant working atmosphere and my supervisor Prof. Dr. Oliver Bringmann for all the invaluable inputs, suggestions, and support throughout this work to make this a success.

I would like to specially thank Prof. Dr. Joachim Gerlach for taking time to review my work and supporting me in the dissertation formalities.

My most grateful thanks are reserved for my parents, Laxminarayana and Vimala Rani, for their continued love and support. Finally, a special to my loving wife, Soumya, for being my inspiration and motivation through what has been an arduous project of my life till now. I am forever grateful for my caring, patient, and supportive family.

## TABLE OF CONTENTS

| DECLARATION                                                  | III |

|--------------------------------------------------------------|-----|

| KURZFASSUNG                                                  | v   |

| ABSTRACT                                                     | 1   |

| PREFACE                                                      | 3   |

| ACKNOWLEDEGEMENT                                             | 4   |

| LIST OF FIGURES                                              | 10  |

| 1 INTRODUCTION                                               | 1   |

| 1.1 Robust Motion Control Systems                            | 1   |

| 1.1.1 Traditional Development                                | 2   |

| 1.1.2 Design and Validation Challenges, Parallel Development | 3   |

| 1.1 Research Contributions                                   | 6   |

| 1.2 Thesis Outline                                           | 7   |

| 2 BACKGROUND                                                 | 9   |

| 2.1 Electronic System Level (ESL)                            | 9   |

| 2.1.1 ESL Design Methodology                                 | 9   |

| 2.1.2 System Level Design using SystemC                      | 10  |

| 2.1.3 Virtual Prototypes                                     | 11  |

| 2.2 Digital Component Modeling                               | 14  |

| 2.2.1 Introduction                                           | 14  |

| 2.2.2 Transaction Level Modeling (TLM)                       | 14  |

| 2.3 Analog and Mixed-Signal (AMS) Modeling                   | 19  |

| 2.3.1 Introduction                                           | 19  |

| 2.3.2 Analog and Mixed-Signal Modeling Languages             | 19  |

| 2.4 Model-Based Design and In-the-loop Technologies          | 23  |

| 2.4.1 Model-in-the-loop (MIL)                                | 26 |

|--------------------------------------------------------------|----|

| 2.4.2 Software-in-the-loop (SIL)                             | 26 |

| 2.4.3 Processor-in-the-loop (PIL)                            | 27 |

| 2.4.4 Hardware-in-the-loop (HIL)                             | 28 |

| 2.4.5 Virtual Hardware-in-the-loop (vHIL)                    | 30 |

| 2.5 Fault Injection and Simulation                           | 31 |

| 2.5.1 Fault Classification on Temporal Behaviour             | 31 |

| 2.5.2 Fault Injection Current Techniques                     | 32 |

| 2.6 Functional Safety Standards                              | 34 |

| 2.6.1 IEC61508                                               | 34 |

| 2.6.2 ISO 26262                                              | 35 |

| 3 STATE-OF-THE-ART AND RESEARCH CONTEXT                      | 37 |

| 3.1 Related work                                             | 37 |

| 3.2 Motion Control Systems (MCS)                             | 40 |

| 3.3 Exemplary Faults in MCS                                  | 43 |

| 3.3.1 Exemplary Faults in the Analog Hardware                | 43 |

| 3.3.2 Exemplary Faults in Mixed-Digital/Analog Hardware      | 44 |

| 3.3.3 Exemplary Faults in the Communication Bus              | 45 |

| 3.3.4 Exemplary Faults in the Software                       | 46 |

| 3.3.5 Exemplary Faults in the Application                    | 46 |

| 3.3.5 Hardware Induced Software Errors                       | 47 |

| 3.4 Fault Injection using Virtual Prototypes                 | 48 |

| 3.5 Aim of the Research and its Objectives                   | 48 |

| 3.6 Drawbacks of Existing Solutions and Research Methodology | 49 |

| 4 MULTI-DOMAIN FAULT MODELING AND SIMULATION                 | 50 |

| 4.1 Introduction                                             | 50 |

| 4.2 Virtual Stress Tests                                     | 52 |

| 4.2.1 Fault Scenario Identification and Fault Specification  | 52 |

| 4.2.2 Identifying Critical System States                                      | 56  |

|-------------------------------------------------------------------------------|-----|

| 4.3 Analog and Mixed-Signal Fault Modeling                                    | 57  |

| 4.3.1 SystemC-AMS and MATLAB/Simulink                                         | 59  |

| 4.3.2 Abstract Fault Models and Fault Interface Design                        | 60  |

| 4.3.3 Fault Simulation in Abstract Models                                     | 62  |

| 4.4 Fault Transfer                                                            | 63  |

| 4.4.1 Motor Control Application                                               | 64  |

| 4.4.2 Examples of Fault Transfer                                              | 67  |

| 4.5 Digital Fault Modeling based on TLM                                       | 95  |

| 4.5.1 State-of-the-art                                                        | 95  |

| 4.5.2 Fault Injection for TLM Abstraction                                     | 96  |

| 4.5.3 Fault Interface Design and Injector                                     | 98  |

| 4.6 Multi-Domain Virtual Platform                                             | 101 |

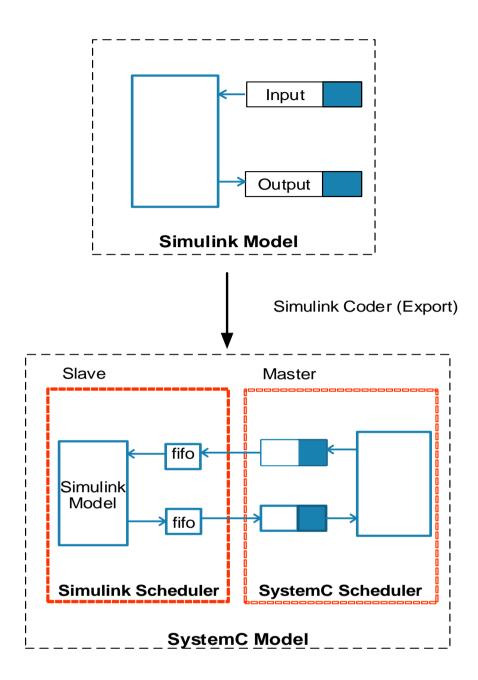

| 4.6.1 Preparing the Simulink Models for Fault Injection                       | 101 |

| 4.6.2 Simulink Model Integration                                              | 102 |

| 4.6.3 Generic Fault Injector                                                  | 105 |

| 4.6.4 Mapping Fault ID's                                                      | 107 |

| 4.7 Automated Fault Injection Tests and Results Evaluation                    | 107 |

| 4.7.1 Motivation                                                              | 107 |

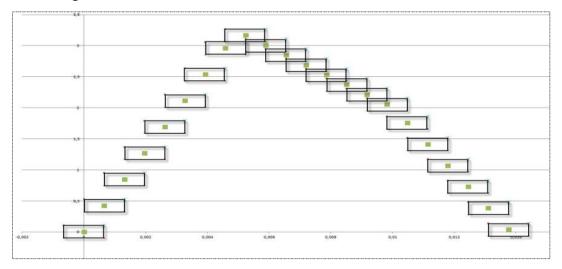

| 4.7.2 Automated Comparison of the Simulation Results of Fault Injection Tests | 108 |

| 4.7.3 Post-Processing Scripting                                               | 109 |

| 5 IMPLEMENTATION ASPECTS AND RESULTS                                          | 110 |

| 5.1 Industrial Motor Control Application                                      | 111 |

| 5.1.1 Control Software                                                        | 111 |

| 5.1.2 PWM Generator                                                           | 112 |

| 5.1.3 Simscape Power electronics                                              | 113 |

| 5.1.4 Simulink Power electronics                                              | 114 |

| 5.1.5 Motor Module                                               | 117 |

|------------------------------------------------------------------|-----|

| 5.2 Simulation Performance Test                                  | 119 |

| 5.3 Automated Fault Injection Tests and Results Evaluation       | 121 |

| 5.3.1 Automated Simulations using Tcl Scripts                    | 121 |

| 5.3.2 Configuration Strategy                                     | 121 |

| 5.3.3 Simulation Control Scripting                               | 122 |

| 5.3.4 Automated Fault Injection Tests                            | 122 |

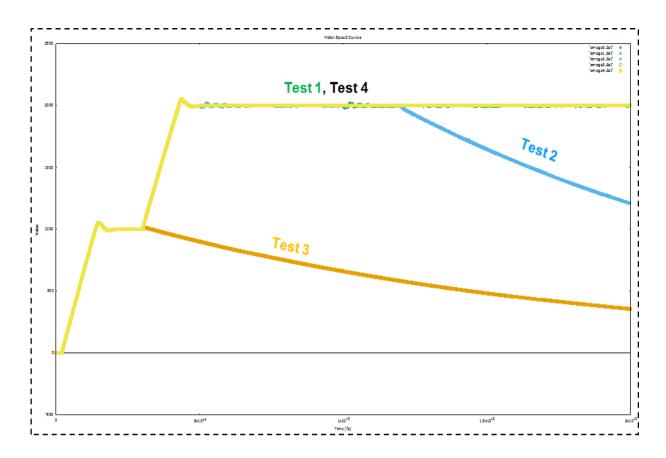

| 5.3.5 Example                                                    | 123 |

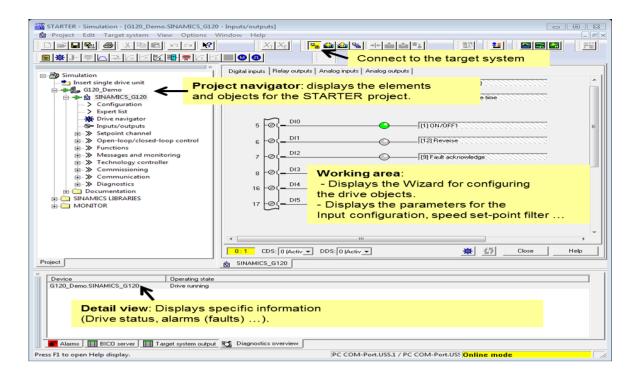

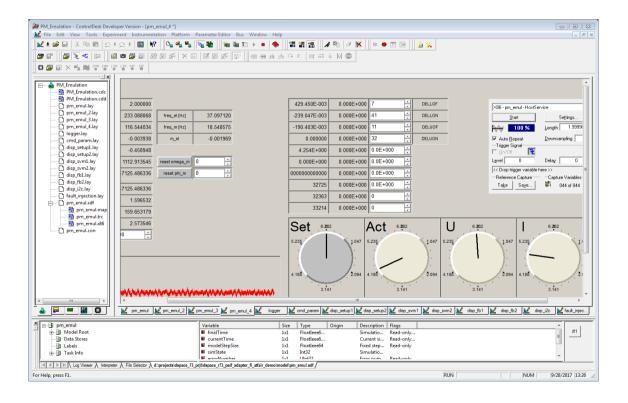

| 5.3.6 Conclusion                                                 | 126 |

| 6 MOTION CONTROL SYSTEM: CASE STUDIES                            | 127 |

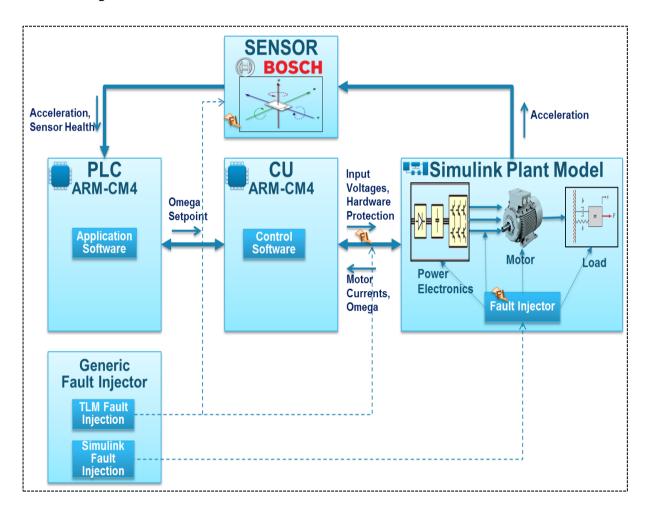

| 6.1 Motor Condition Monitoring using Acceleration Sensor from RB | 128 |

| 6.1.1 Setup                                                      | 128 |

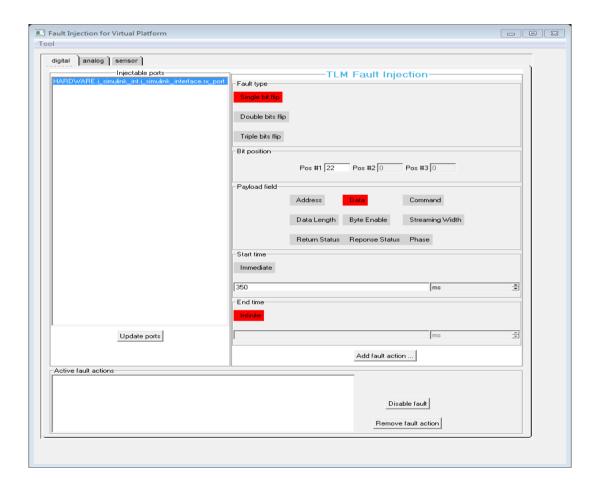

| 6.1.2 Fault Injection GUI                                        | 129 |

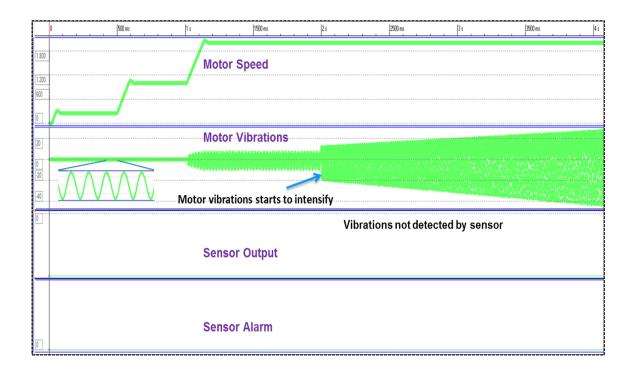

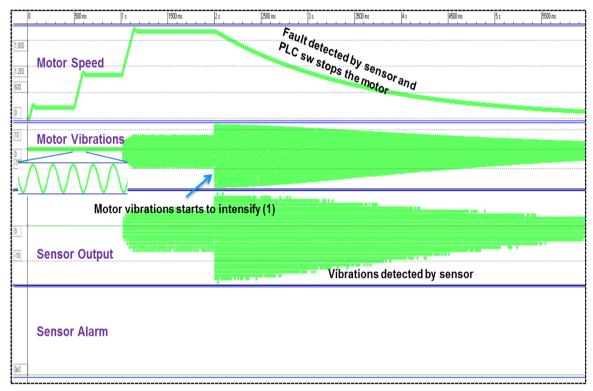

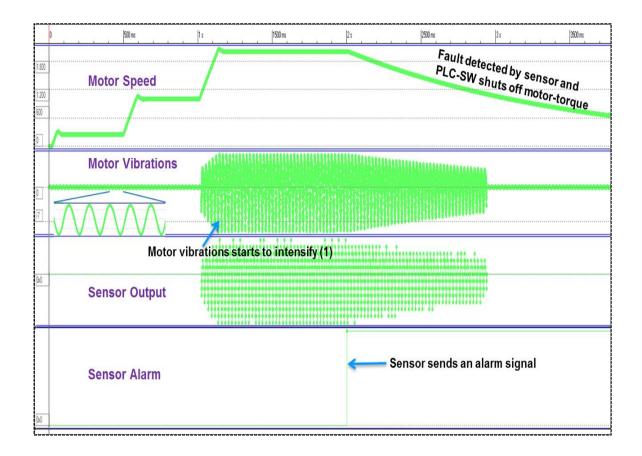

| 6.1.3 Test Scenario's                                            | 130 |

| 6.1.4 Conclusion                                                 | 133 |

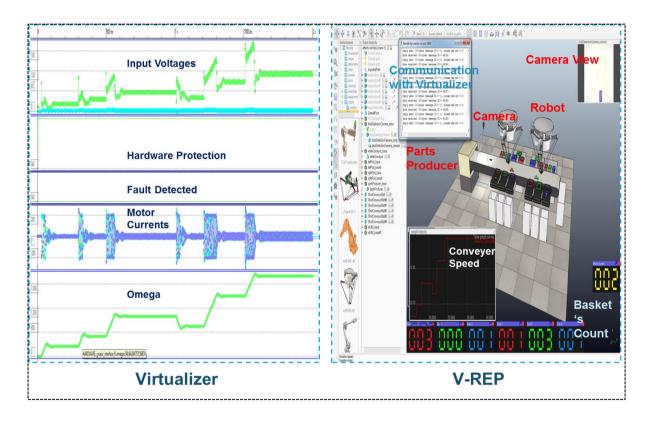

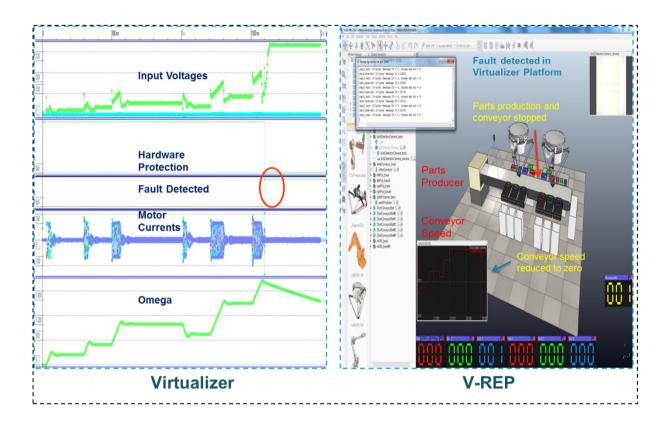

| 6.2 Conveyer-Belt Simulation using V-REP Simulator               | 134 |

| 6.2.1 Setup                                                      | 134 |

| 6.2.2 Test Scenario's                                            | 136 |

| 6.2.3 Conclusion                                                 | 138 |

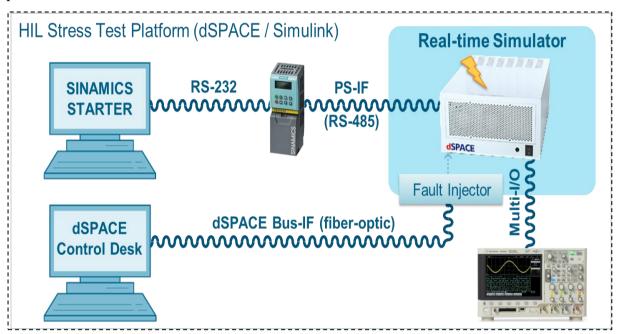

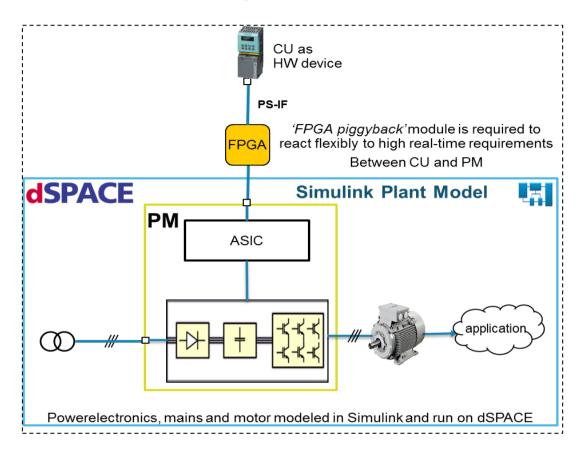

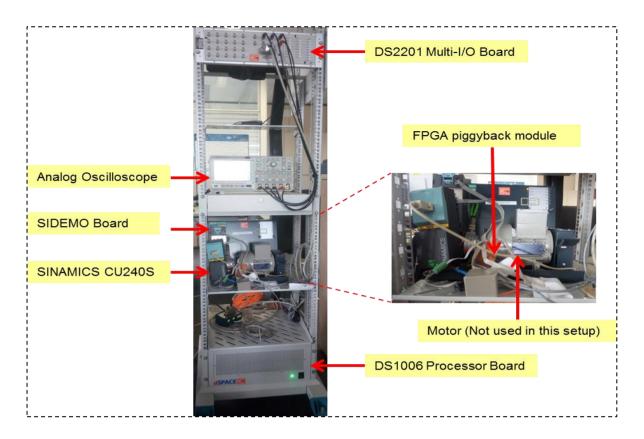

| 6.3 Hardware-in-the-loop (HIL)                                   | 138 |

| 6.3.1 Setup                                                      | 139 |

| 6.3.2 Characteristics of the Setup                               | 141 |

| 6.3.3 Fault Injection                                            | 142 |

| 6.3.4 Conclusion                                                 | 145 |

| 7 CONCLUSION AND OUTLOOK                                         | 146 |

| 7.1 Summary                                                      | 146 |

| 7.2 Contributions                                                | 147 |

| 7.2.1 Fault Injection in Heterogeneous Component Models          | 147 |

|------------------------------------------------------------------|-----|

| 7.2.2 Fault Transfer                                             | 148 |

| 7.2.3 Automated Stress Tests and Post Processing                 | 148 |

| 7.2.4 Case Studies of Motion Control System                      | 149 |

| 7.3 Outlook                                                      | 149 |

| 7.3.1 ASAM XIL Standard for Fault Effect Simulation              | 149 |

| 7.3.2 Improved Workflow for Virtual Prototypes with Stress Tests | 150 |

| REFERENCES                                                       | 151 |

# LIST OF FIGURES

| Figure 1: Typical Motion Control System with Sensor, PLC and CU [3]                    | 2  |

|----------------------------------------------------------------------------------------|----|

| Figure 2: Traditional Product Development Flow                                         | 3  |

| Figure 3: Hardware/Software Parallel Development                                       | 4  |

| Figure 4: SystemC language architecture [14]                                           | 10 |

| Figure 5: Simulation speed versus accuracy trade-off [13]                              | 15 |

| Figure 6: Use cases and abstraction levels [13]                                        | 16 |

| Figure 7: TLM-2.0 communication [13]                                                   | 17 |

| Figure 8: AMS Extensions for the SystemC Language Standard [9]                         | 20 |

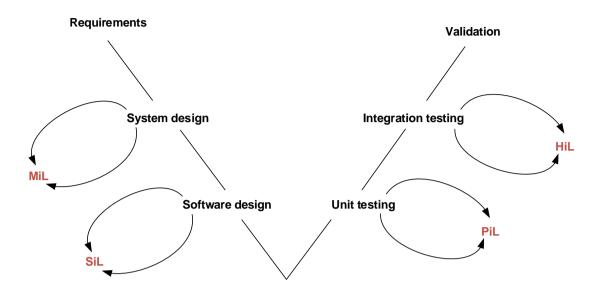

| Figure 9: The V-model of the Systems Engineering Process                               | 24 |

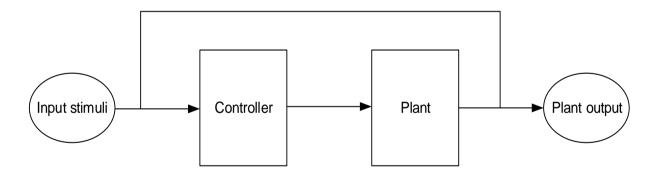

| Figure 10: Typical control system                                                      | 25 |

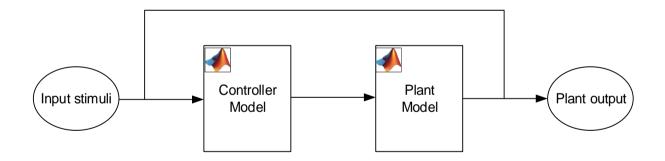

| Figure 11: Model-in-the-loop                                                           | 26 |

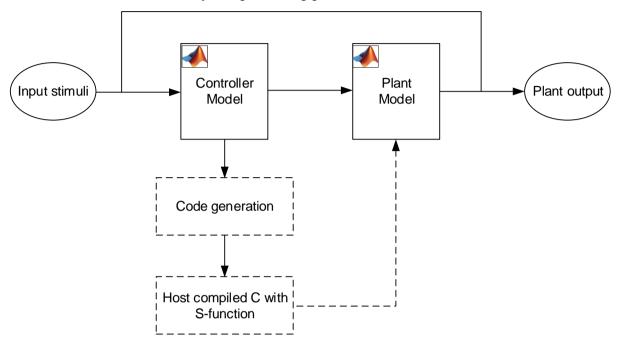

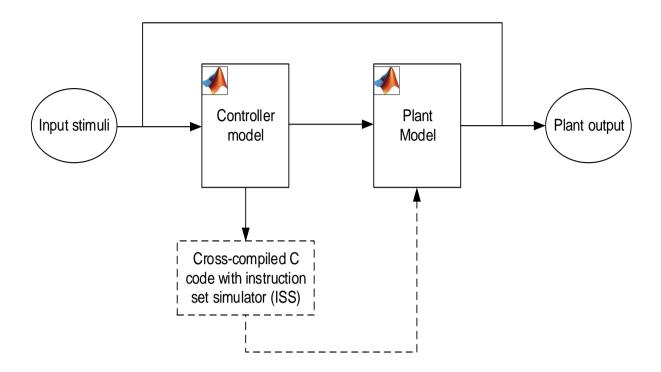

| Figure 12: Software-in-the-loop                                                        | 27 |

| Figure 13: Processor-in-the-loop                                                       | 28 |

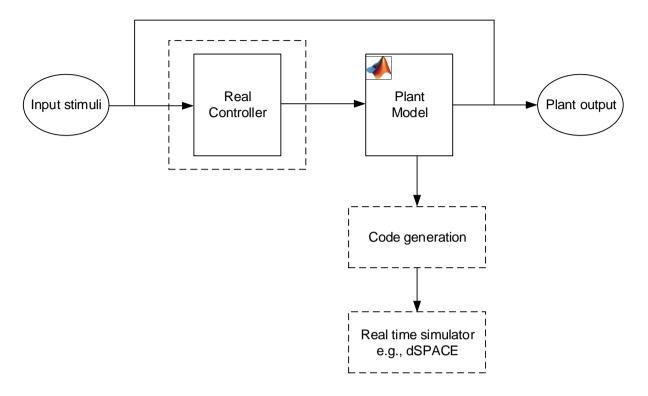

| Figure 14: Hardware-in-the-loop                                                        | 29 |

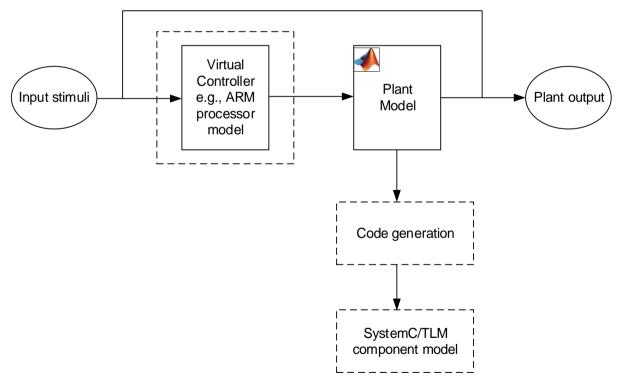

| Figure 15: Virtual Hardware-in-the-loop                                                | 30 |

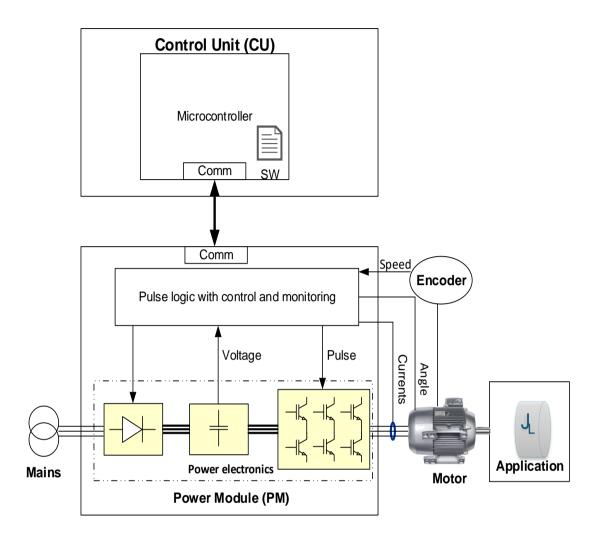

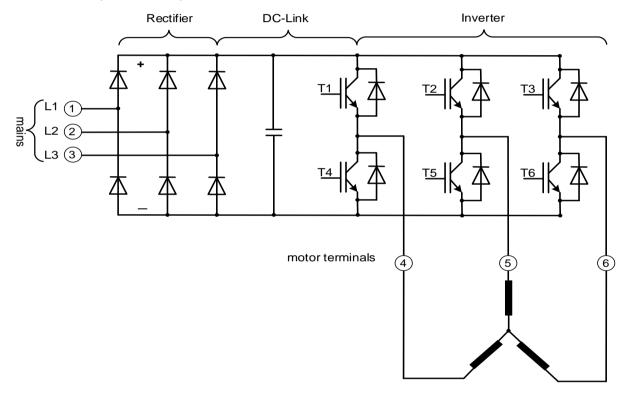

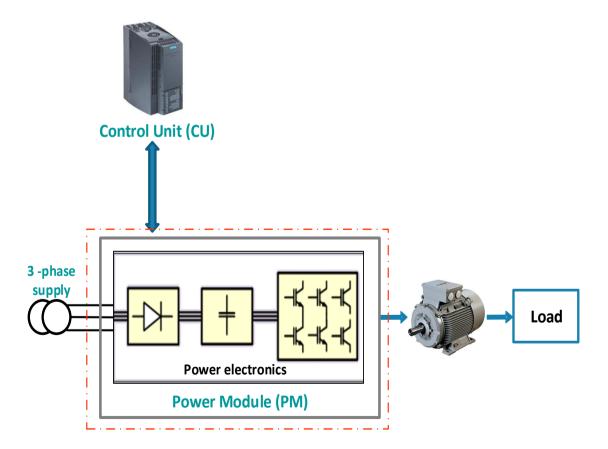

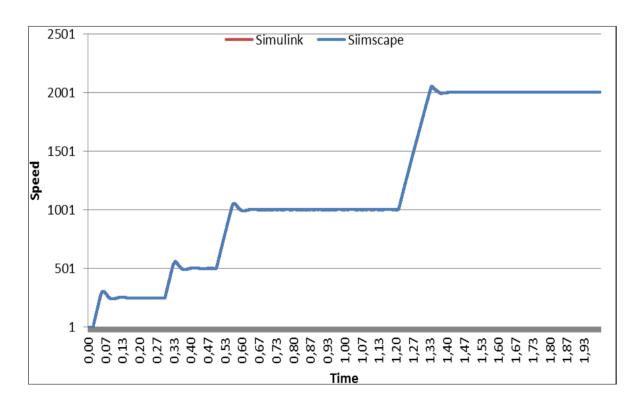

| Figure 16: Drive Model of a Motion Control System                                      | 41 |

| Figure 17: Power electronics of a power module                                         | 42 |

| Figure 18: Fault Scenario Template                                                     | 53 |

| Figure 19: Fault Specification Template                                                | 54 |

| Figure 20: Fault Scenario Example                                                      | 54 |

| Figure 21: Fault Specification Example                                                 | 55 |

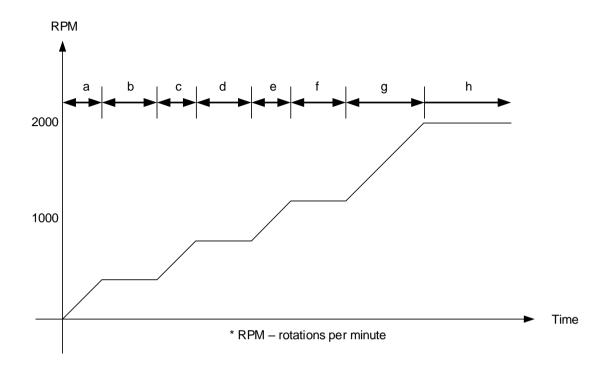

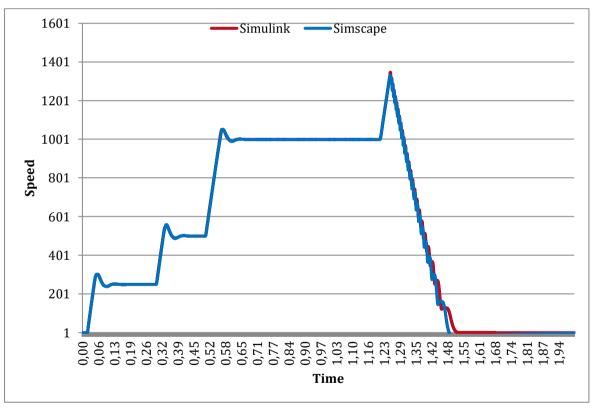

| Figure 22: Speed Profile of a Motor                                                    | 56 |

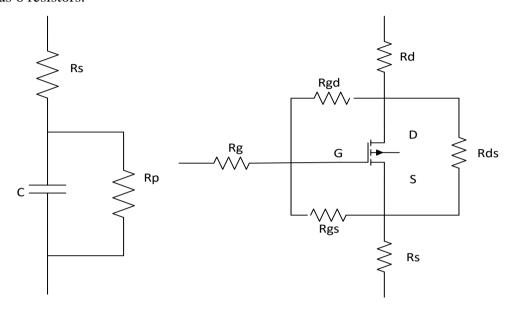

| Figure 23: Fault models of capacitor and transistor                                    | 59 |

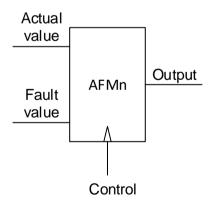

| Figure 24: Analog Fault Model (AFM)                                                    | 60 |

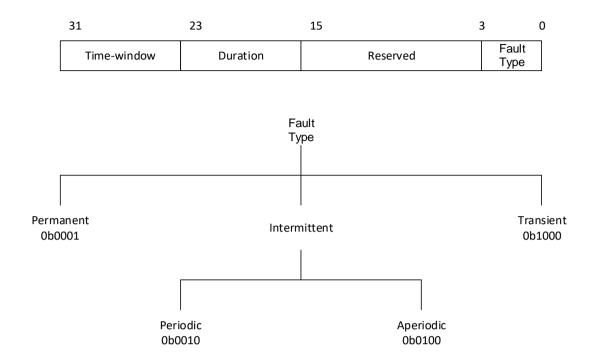

| Figure 25: Control Interface and Fault Type                                            | 62 |

| Figure 26: Motor Control Application Setup                                             | 65 |

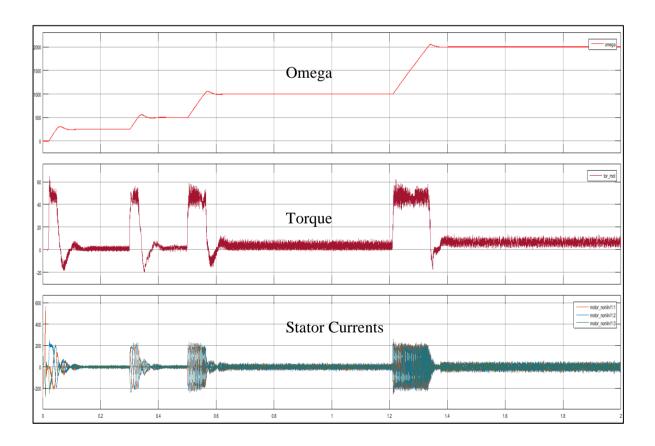

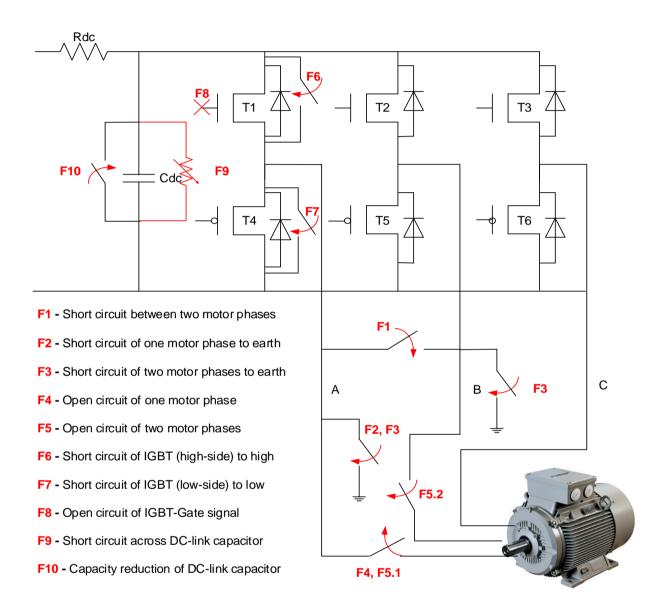

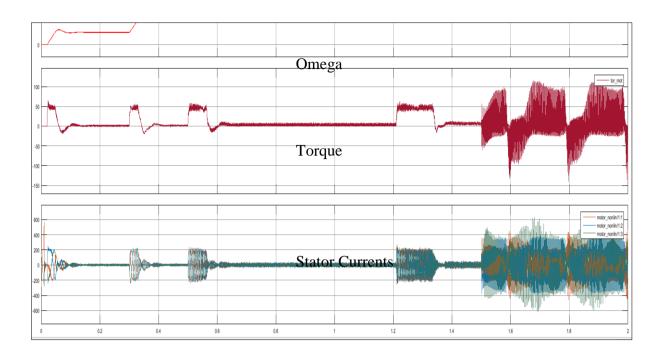

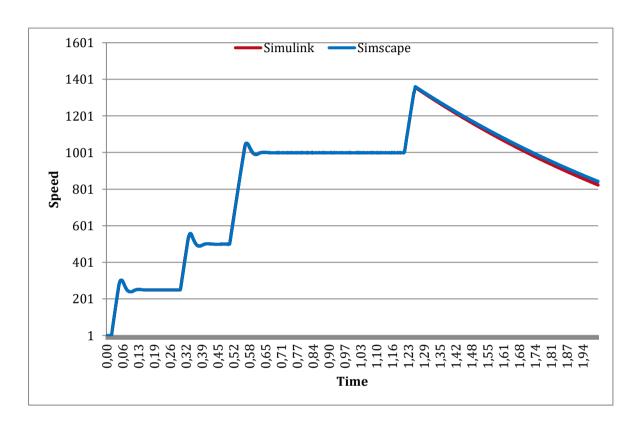

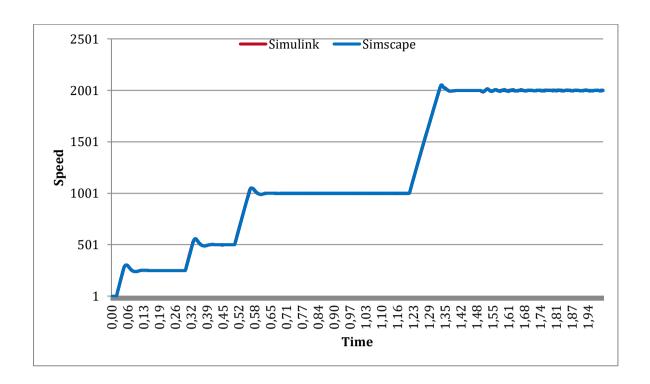

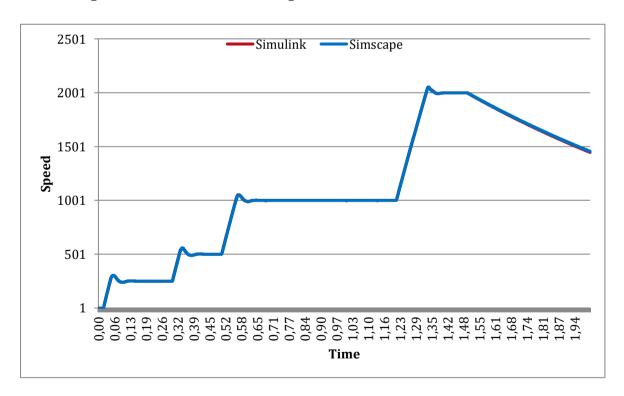

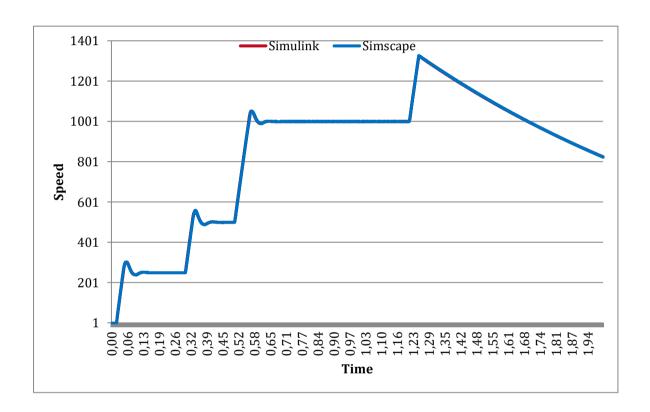

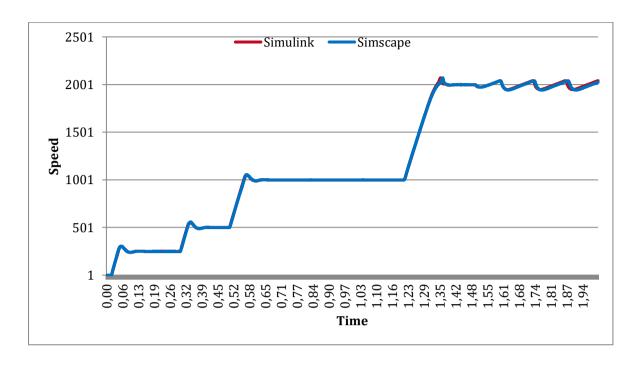

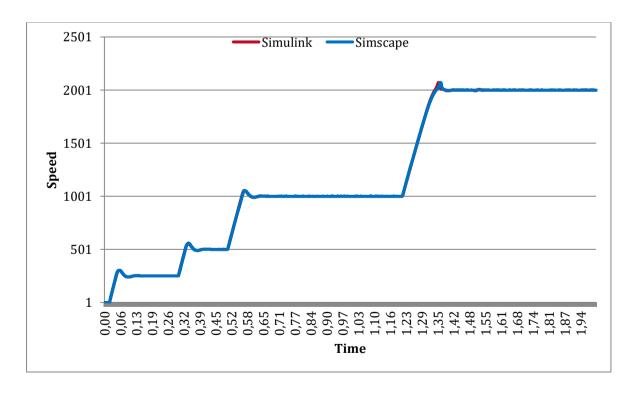

| Figure 27: Simulation Output (Simscape)                                                | 66 |

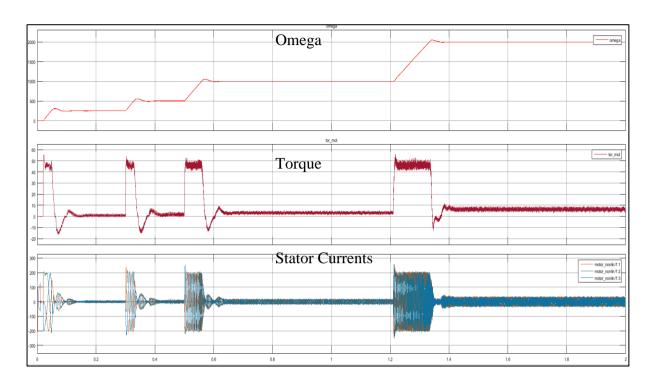

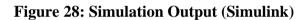

| Figure 28: Simulation Output (Simulink)                                                | 66 |

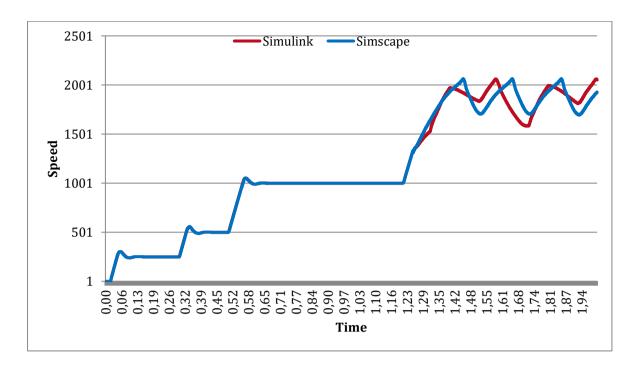

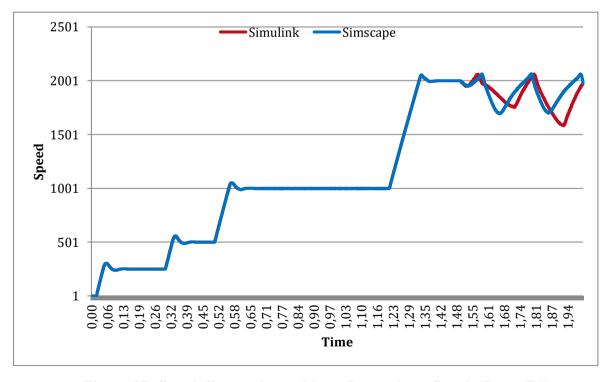

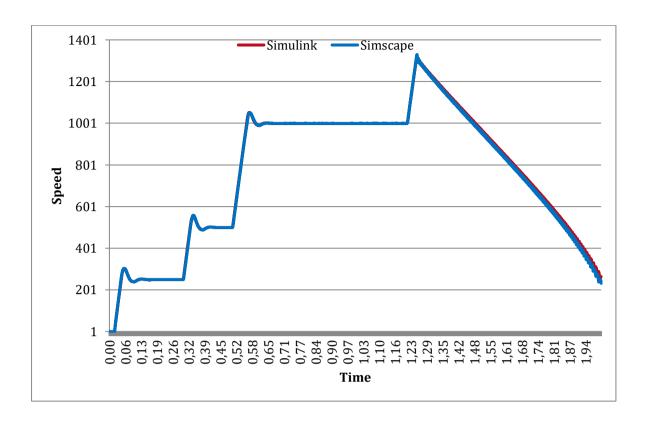

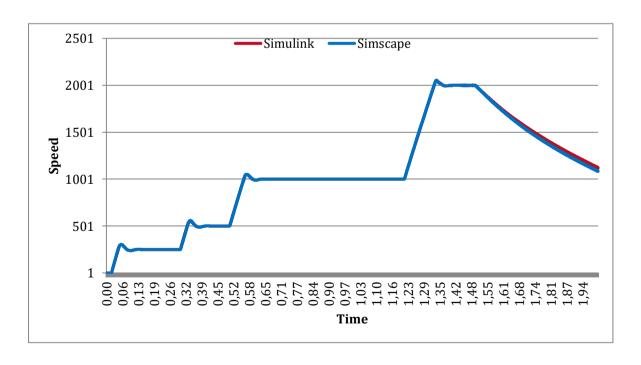

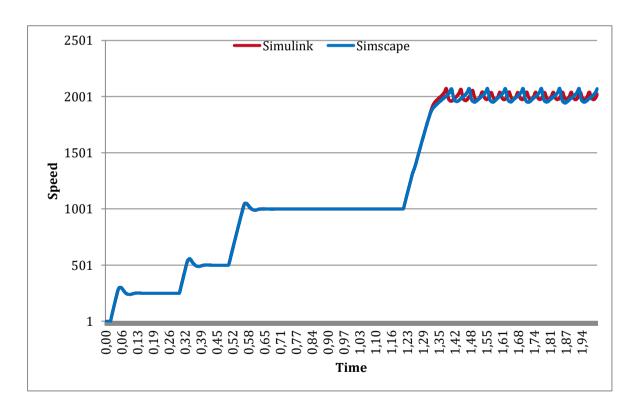

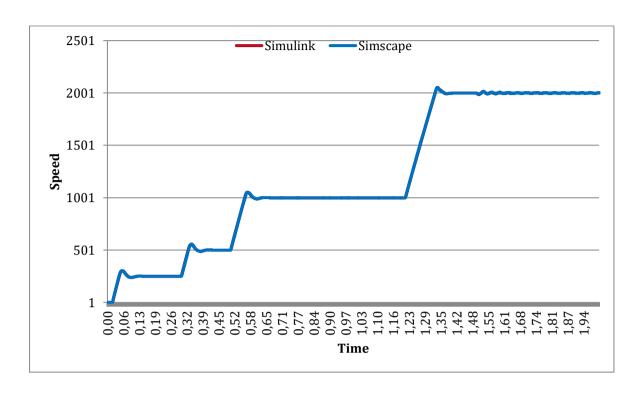

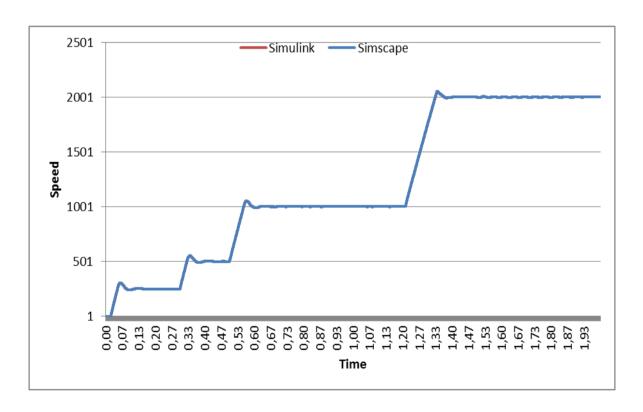

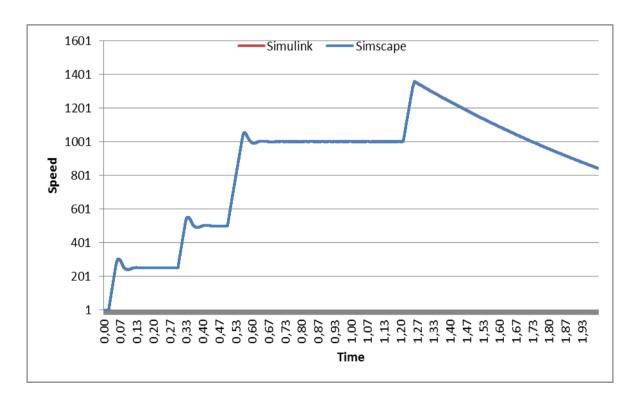

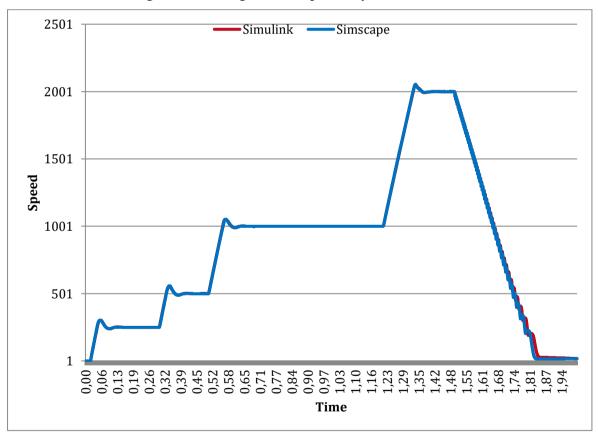

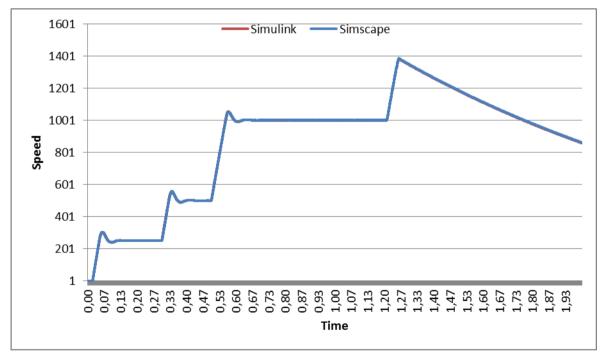

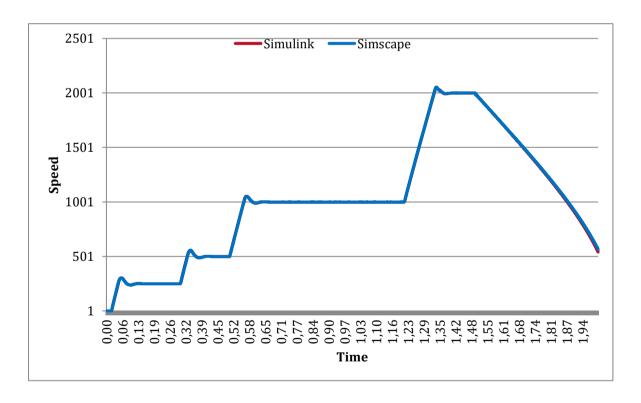

| Figure 29: Speed Comparison                                                            | 67 |

| Figure 30: Fault Selection in Inverter and Motor                                       | 67 |

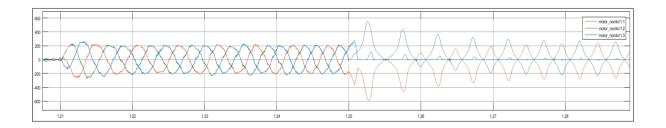

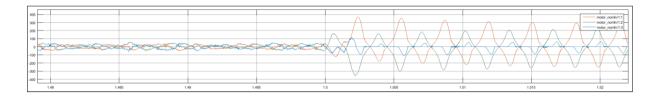

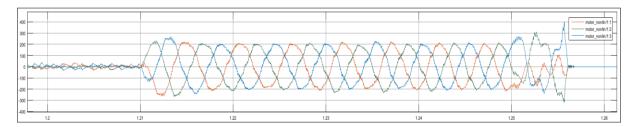

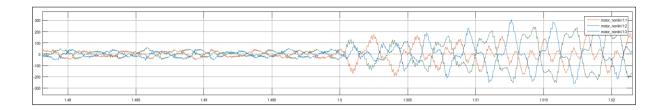

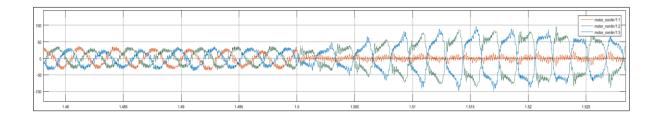

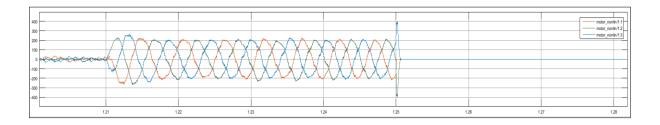

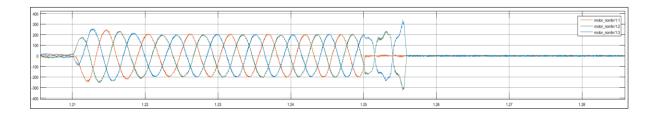

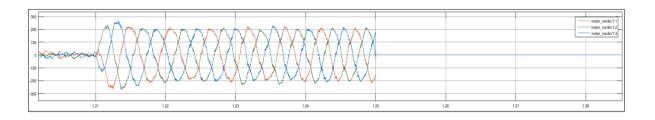

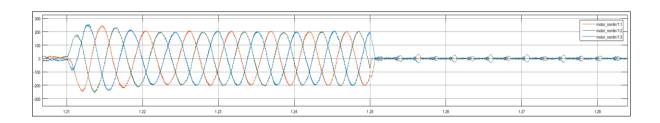

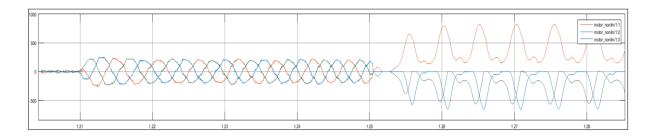

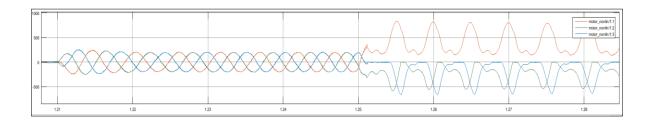

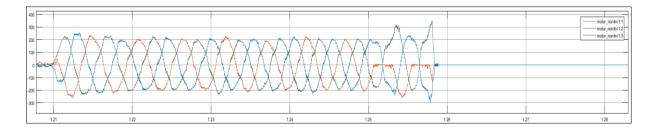

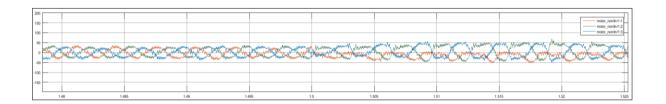

| Figure 31: Simulation Output (Transient State) - Simscape (F1)                         | 69 |

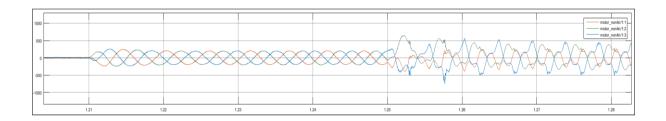

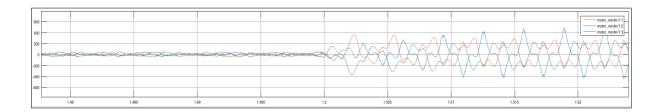

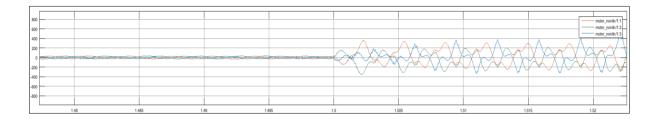

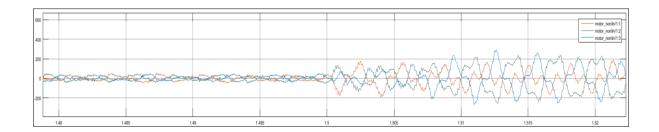

| Figure 32: Motor Currents Zoomed (Transient State) - Simscape (F1)                     | 69 |

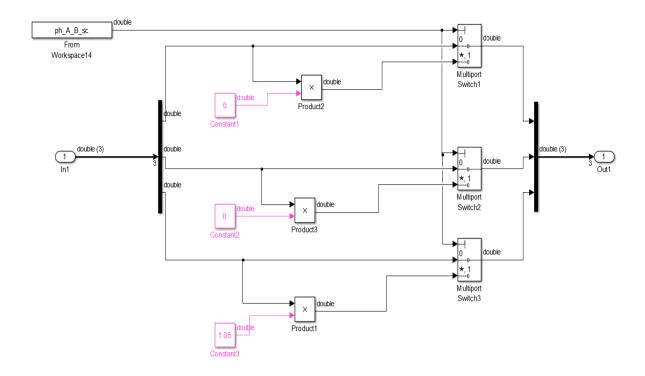

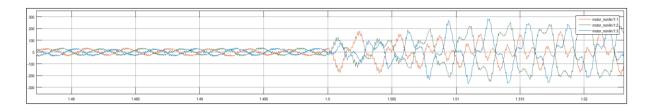

| Figure 33: Phase-to-Phase Short-Circuit Fault Model without Protection - Simulink (F1) | 70 |

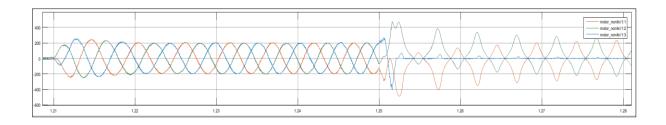

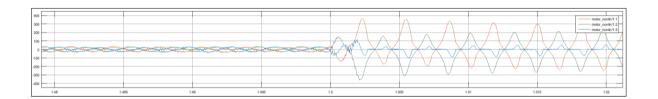

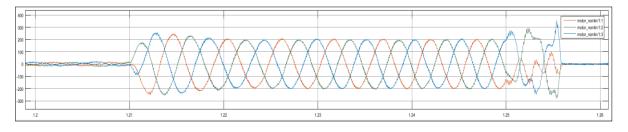

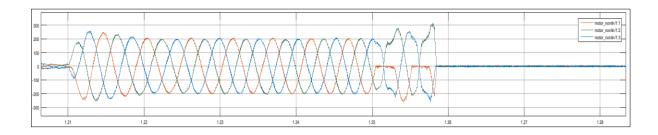

| Figure 34: Simulation Output (Transient State) - Simulink (F1)                         | 71 |

| Figure 35: Motor Currents Zoomed (Transient State) - Simulink (F1)                  | 71 |

|-------------------------------------------------------------------------------------|----|

| Figure 36: Speed Comparison without Protection - Transient State (F1)               | 72 |

| Figure 37: Speed Comparison without Protection - Steady State (F1)                  | 72 |

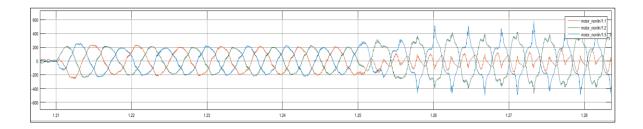

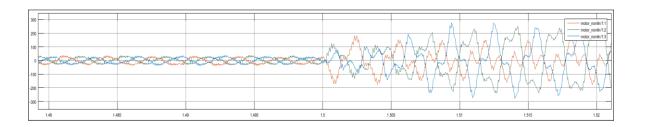

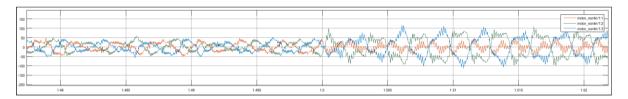

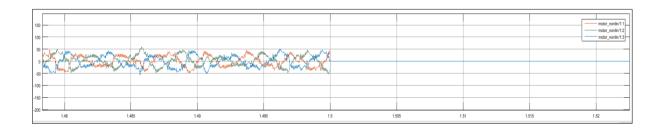

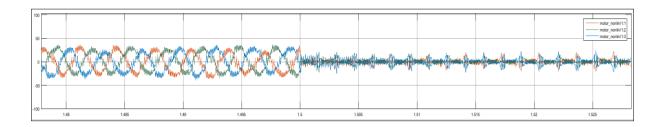

| Figure 38: Motor Currents Zoomed (Steady State) - Simscape (F1)                     | 73 |

| Figure 39: Motor Currents Zoomed (Steady State) - Simulink (F1)                     | 73 |

| Figure 40: Phase-to-Phase Short-Circuit Fault Model with Protection – Simulink (F1) | 74 |

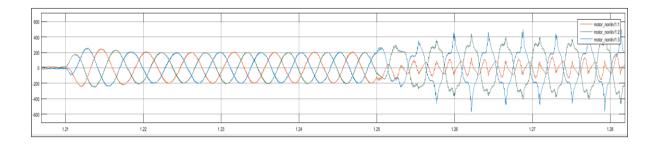

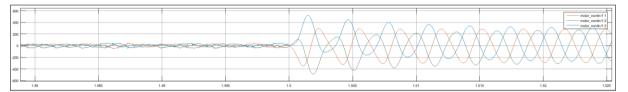

| Figure 41: Motor Currents Zoomed (Transient State) - Simscape (F1)                  | 74 |

| Figure 42: Motor Currents Zoomed (Transient State) - Simulink (F1)                  | 74 |

| Figure 43: Speed Comparison with Protection - Transient State (F1)                  | 75 |

| Figure 44: Speed Comparison with Protection - Steady State (F1)                     | 75 |

| Figure 45: Motor Currents Zoomed (Steady State) - Simscape (F1)                     | 76 |

| Figure 46: Motor Currents Zoomed (Steady State) - Simulink (F1)                     | 76 |

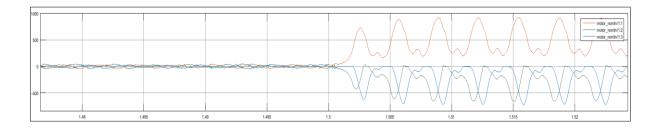

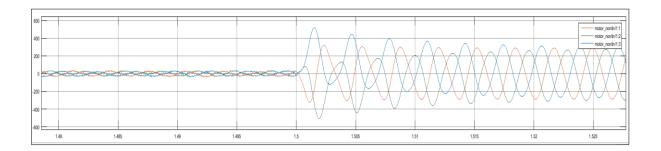

| Figure 47: Motor Currents Zoomed (Transient State) - Simscape (F2)                  | 77 |

| Figure 48: Motor Currents Zoomed (Transient State) - Simulink (F2)                  | 77 |

| Figure 49: Speed Comparison without Protection - Transient State (F2)               | 77 |

| Figure 50: Speed Comparison without Protection - Steady State (F2)                  | 78 |

| Figure 51: Motor Currents Zoomed (Steady State) - Simscape (F2)                     | 78 |

| Figure 52: Motor Currents Zoomed (Steady State) - Simulink (F2)                     | 78 |

| Figure 53: Speed Comparison with Protection - Transient State (F2)                  | 79 |

| Figure 54: Speed Comparison with Protection - Steady State (F2)                     | 80 |

| Figure 55: Motor Currents Zoomed (Transient State) - Simscape (F2)                  | 80 |

| Figure 56: Motor Currents Zoomed (Transient State) - Simulink (F2)                  | 80 |

| Figure 57: Motor Currents Zoomed (Steady State) - Simscape (F2)                     | 81 |

| Figure 58: Motor Currents Zoomed (Steady State) - Simulink (F2)                     | 81 |

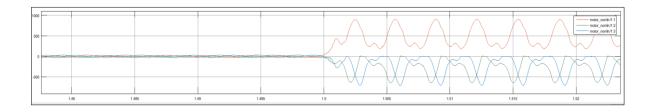

| Figure 59: Speed Comparison with Protection - Steady State (F4)                     | 82 |

| Figure 60: Motor Currents Zoomed (Steady State) - Simscape (F4)                     | 83 |

| Figure 61: Motor Currents Zoomed (Steady State) - Simulink (F4)                     | 83 |

| Figure 62: Speed Comparison with Protection - Transient State (F4)                  | 83 |

| Figure 63: Motor Currents Zoomed (Transient State) - Simscape (F4)                  | 84 |

| Figure 64: Motor Currents Zoomed (Transient State) - Simulink (F4)                  | 84 |

| Figure 65: Speed Comparison with Protection - Steady State (F5)                     | 84 |

| Figure 66: Speed Comparison with Protection - Transient State (F5)                  | 85 |

| Figure 67: Motor Currents Zoomed (Steady State) - Simscape (F5)                     | 85 |

| Figure 68: Motor Currents Zoomed (Steady State) - Simulink (F5)                     | 86 |

| Figure 69: Motor Currents Zoomed (Transient State) - Simscape (F5)                  | 86 |

| Figure 70: Motor Currents Zoomed (Transient State) - Simulink (F5)                  | 86 |

| Figure 71: Motor Currents Zoomed (Transient State) - Simscape (F6)                  | 87 |

| Figure 72: Speed Comparison with Protection - Transient State (F6)                  | 87 |

| Figure 73: Motor Currents Zoomed (Transient State) - Simulink (F6)                  | 88 |

| Figure 74: Speed Comparison with Protection - Steady State (F6)                              | 88  |

|----------------------------------------------------------------------------------------------|-----|

| Figure 75: Motor Currents Zoomed (Steady State) - Simscape (F6)                              | 89  |

| Figure 76: Motor Currents Zoomed (Steady State) - Simulink (F6)                              | 89  |

| Figure 77: Motor Currents Zoomed (Transient State) - Simscape (F8)                           | 89  |

| Figure 78: Motor Currents Zoomed (Transient State) - Simulink (F8)                           | 90  |

| Figure 79: Speed Comparison with Protection - Transient State (F8)                           | 90  |

| Figure 80: Motor Currents Zoomed (Steady State) - Simscape (F8)                              | 91  |

| Figure 81: Motor Currents Zoomed (Steady State) - Simulink (F8)                              | 91  |

| Figure 82: Speed Comparison with Protection - Steady State (F8)                              | 91  |

| Figure 83: Motor Currents Zoomed (Steady State) - Simscape (F9)                              | 92  |

| Figure 84: Speed Comparison with Protection - Steady State (F9)                              | 92  |

| Figure 85: Motor Currents Zoomed (Steady State) - Simulink (F9)                              | 93  |

| Figure 86: Speed Comparison - Steady State (F10 - 50 % Reduction)                            | 94  |

| Figure 87: Speed Comparison - Steady State (F10 - 20 % Reduction)                            | 94  |

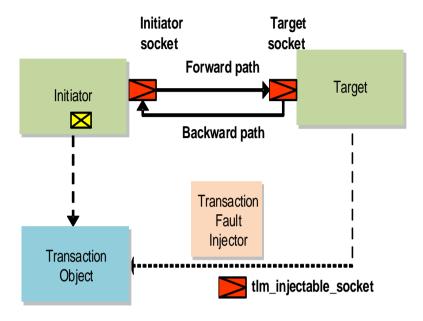

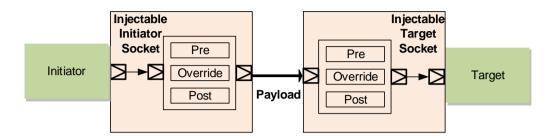

| Figure 88: TLM Injectable Socket                                                             | 97  |

| Figure 89: TLM Injectable Socket Block Diagram [13]                                          | 98  |

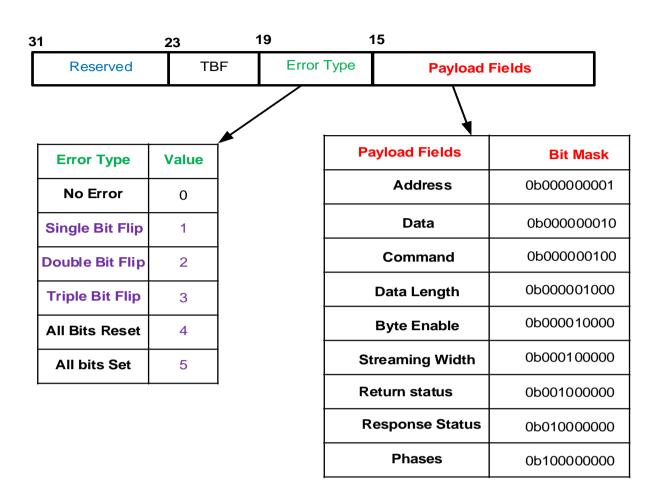

| Figure 90: Fault Class Information                                                           | 99  |

| Figure 91: Bit Position Information                                                          | 99  |

| Figure 92: Fault Injection Examples                                                          | 100 |

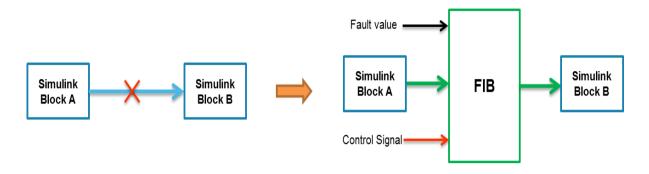

| Figure 93: Normal Line                                                                       | 101 |

| Figure 94: Branched Line                                                                     | 101 |

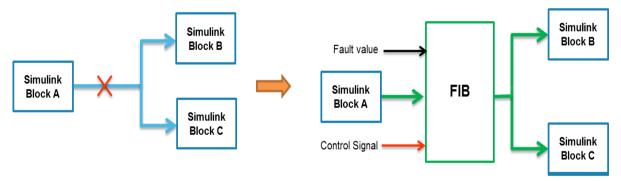

| Figure 95: Simulink System with Connector Blocks to Interface to SystemC                     | 102 |

| Figure 96: Exporting Simulink to SystemC                                                     | 104 |

| Figure 97: Example of an interpolated reference curve with the assigned tolerance rectangles | 108 |

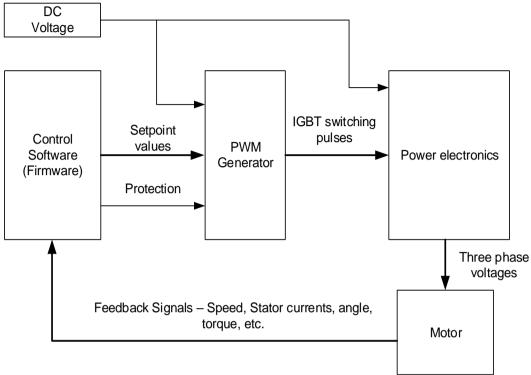

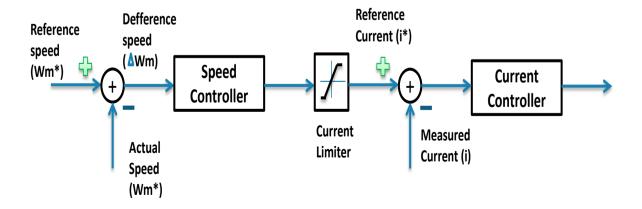

| Figure 98: Motor Control Application Block Diagram                                           | 111 |

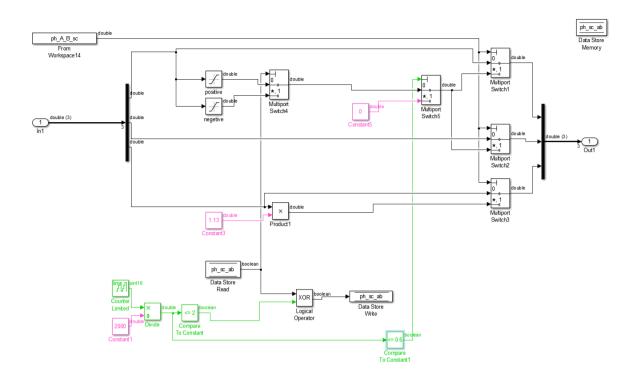

| Figure 99: Control Software                                                                  | 112 |

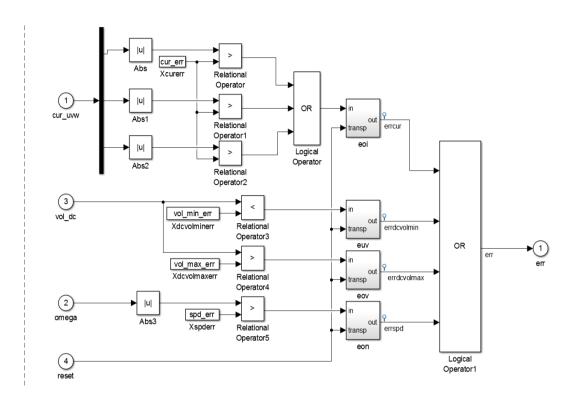

| Figure 100: Protection Mechanisms                                                            | 112 |

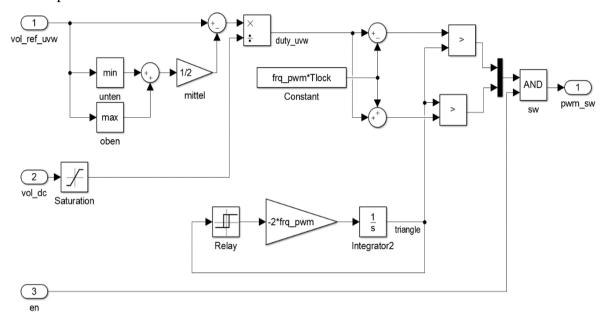

| Figure 101: PWM Generator                                                                    | 113 |

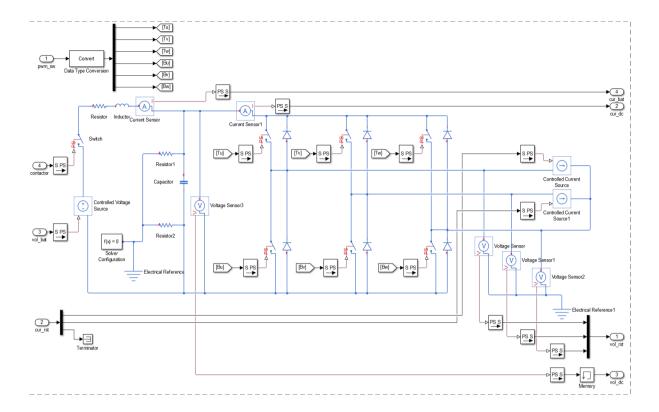

| Figure 102: Power electronics (Simscape)                                                     | 114 |

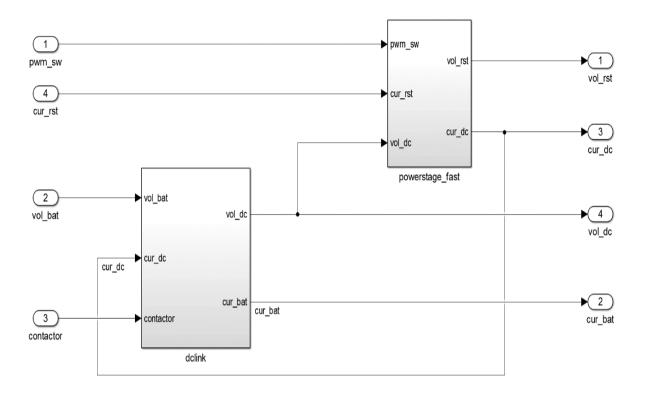

| Figure 103: LC filter, DC link and Inverter (Simulink)                                       | 115 |

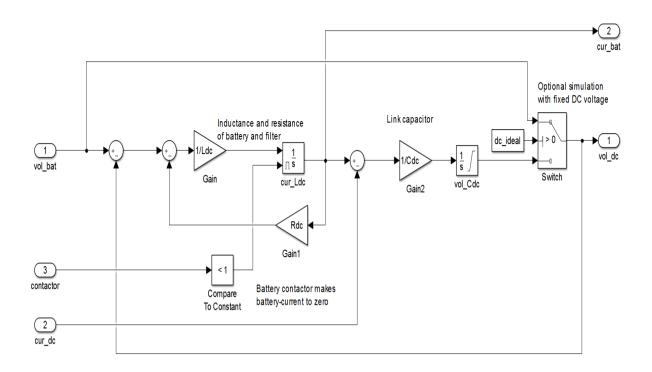

| Figure 104: LC filter + DC-link (Simulink)                                                   | 116 |

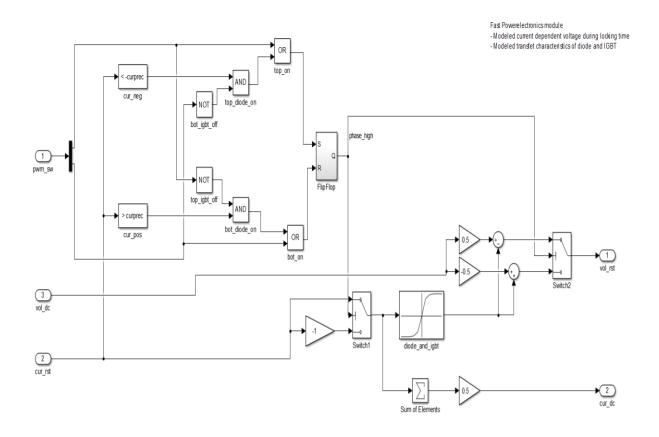

| Figure 105: Inverter module (Simulink)                                                       | 117 |

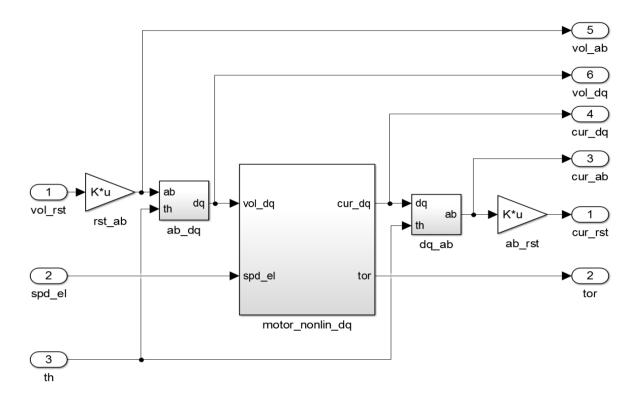

| Figure 106: Synchronous Motor                                                                | 118 |

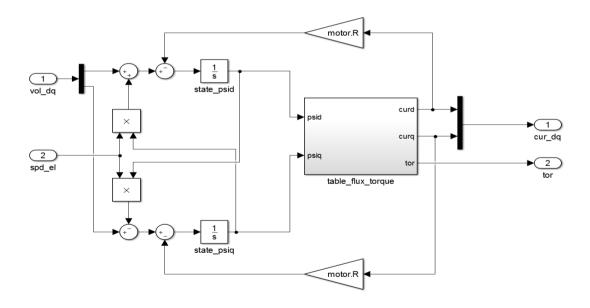

| Figure 107: Motor in dq-coordinates                                                          | 118 |

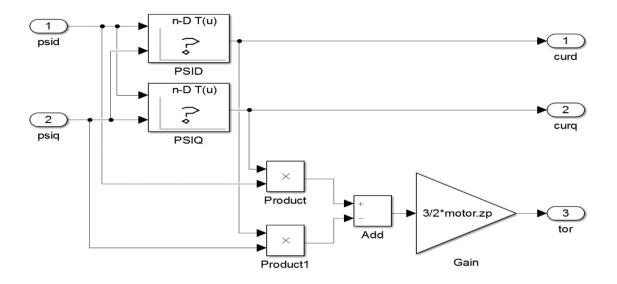

| Figure 108: Flux-Torque table                                                                | 119 |

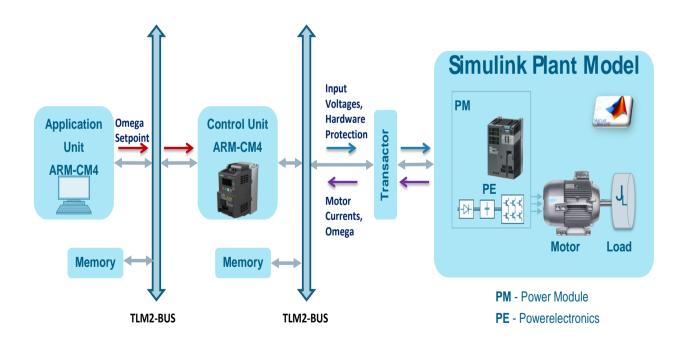

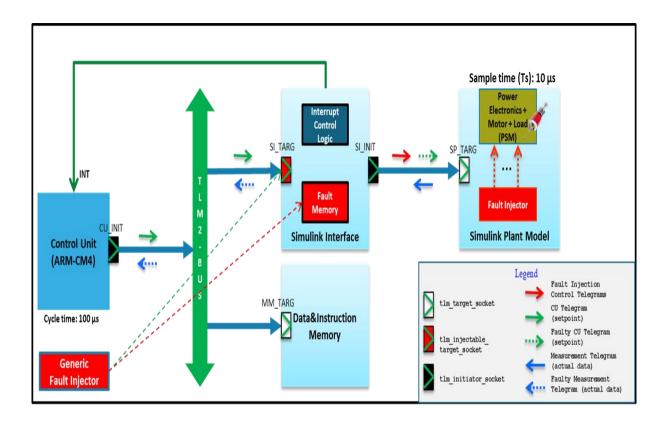

| Figure 109: Simulation Platform                                                              | 119 |

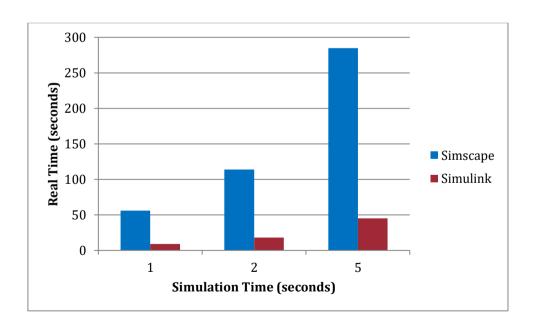

| Figure 110: Simulation Performance                                                           | 120 |

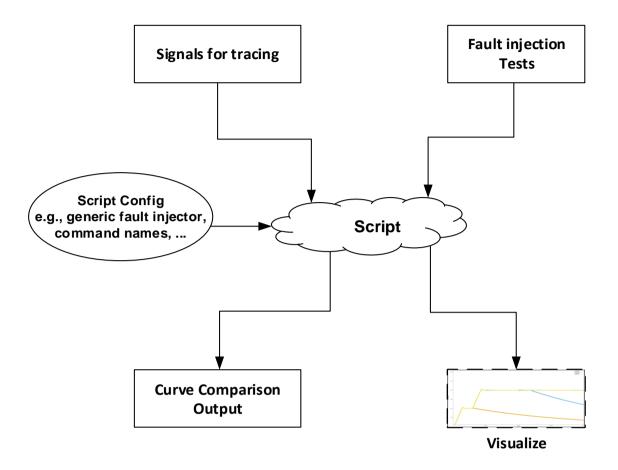

| Figure 111: TCL Script                                                                       | 123 |

| Figure 112: Virtual Drive Platform for Fault Simulation                                      | 124 |

| Figure 113: Format for Fault Injection Tests                                  | 124 |

|-------------------------------------------------------------------------------|-----|

| Figure 114: Motor Speed Output                                                | 125 |

| Figure 115: Curve Comparison Output                                           | 126 |

| Figure 116: Simulation Platform for Motor Condition Monitoring                | 128 |

| Figure 117: Fault Injection GUI                                               | 129 |

| Figure 118: Scenario 1 - Simulation Output                                    | 131 |

| Figure 119: Scenario 2 - Simulation Output                                    | 132 |

| Figure 120: Scenario 3 - Simulation Output                                    | 133 |

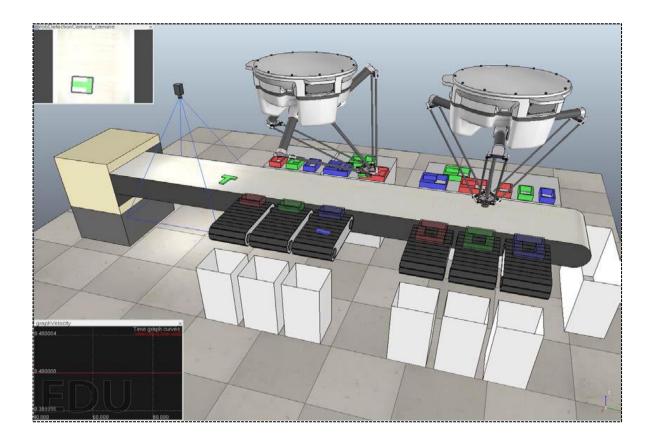

| Figure 121: Simulation Platform with Belt-conveyor                            | 134 |

| Figure 122: Virtual Conveyor Belt                                             | 135 |

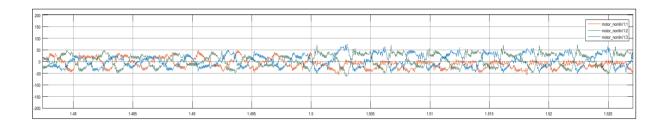

| Figure 123: Simulation Output without Fault Injection                         | 136 |

| Figure 124: Simulation Output with Fault Injection                            | 137 |

| Figure 125: HIL Setup with SINAMICS G120 with CU240 and PM240                 | 139 |

| Figure 126: CU Hardware with Virtual PM                                       | 141 |

| Figure 127: HIL Demonstrator Setup                                            | 142 |

| Figure 128: SINAMICS STARTER User Interface                                   | 143 |

| Figure 129: ControlDesk Experiment                                            | 143 |

| Figure 130: Fault detected in SINAMICS STARTER                                | 144 |

| Figure 131: Motor Voltages and Currents measured using an Analog Oscilloscope | 145 |

|                                                                               |     |

This page is intentionally left blank.

## 1 Introduction

## 1.1 Robust Motion Control Systems

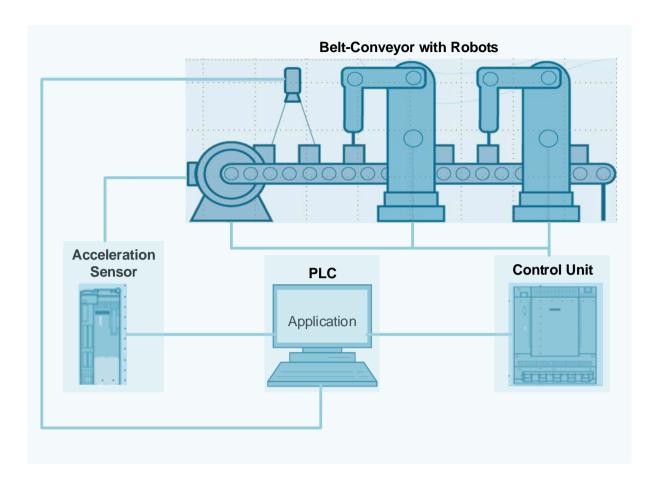

Production plants of the future for industrial production 4.0 [1] [2], are highly complex, intelligent systems that consist of a variety of heterogeneous components: software, microelectronics, power electronics, sensor technology and actuators. A typical motion control system shown in Figure 1 in which the conveyor belt and robotic arms are coordinated for fast and very precise position and path control to pick and sort the items moving on the belt-conveyor.

The basic components in a typical motion control system are the application controller (PLC – Programmable Logic Controller), the drive (the control unit (CU) along with power electronics), the motor, the mechanical elements, and the feedback device or position sensor. The path planning or trajectory calculations are performed in the PLC, which sends lowvoltage command signals to the drive, which in turn applies the necessary voltage and current to the motor, resulting in the desired motion. Sometimes feedback devices on the motor or the belt-conveyor are used to notify the drive or the controller with specific details about the actual movement of the motor shaft or the belt-conveyor. This feedback data is used to increase the accuracy of the motion, and can be used to compensate for dynamic changes that may occur on the belt-conveyor. The robot-arms are required to pick "on-the-fly" objects moving on conveyor belts; the instantaneous location of moving objects is computed by the vision system acquiring images from a stationary, down looking camera. Motor condition monitoring is constant monitoring of the motor's condition which enables changes in the monitored operating parameters to be recorded at a very early stage of fault development. The acceleration sensor is used for the condition monitoring of the motor to detect vibrations and jerking.

Figure 1: Typical Motion Control System with Sensor, PLC and CU [3]

### 1.1.1 Traditional Development

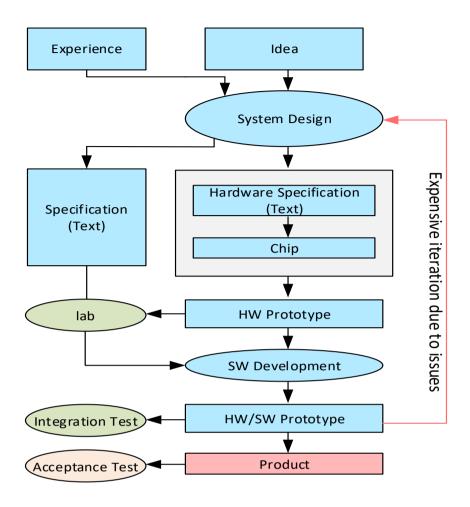

Figure 2 shows the traditional development flow of motion control systems, which was slow paced, sequential and embedded software development was dependent on the availability of physical boards. When the software content of an embedded system was relatively small, it was safe to wait for hardware to become available to start developing the software. Teams that wanted to get started sooner used register-transfer level (RTL) descriptions to represent the hardware, but that process was painfully slow. Register Transfer Level (RTL) abstraction is used to create high-level representations of a circuit, from which lower-level representations and ultimately actual wiring can be derived.

Figure 2: Traditional Product Development Flow

#### 1.1.2 Design and Validation Challenges, Parallel Development

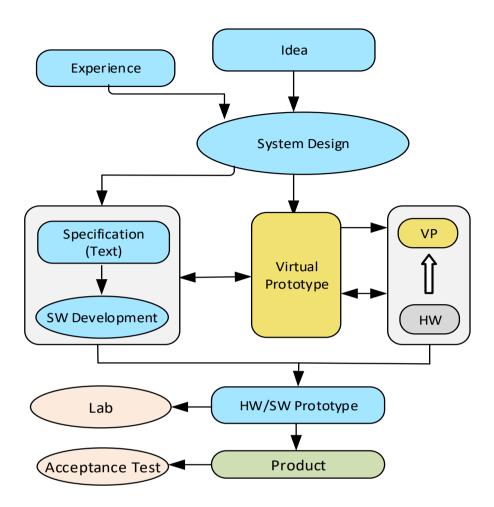

A well-proven way of dealing with the complexity of engineering systems is to find a suitable abstraction level to work with, since at high abstraction level details can be masked or hidden and a big picture view of the system can be achieved, without getting lost in details [3] [4]. Time-to-market pressures and system complexity force reconsideration in how these systems are designed. Systems design companies are increasingly designing at higher levels, which require understanding and validating software earlier in the process. This has led to the hardware/software parallel development i.e., hardware (right) and software (left) are developed parallel as shown in Figure 3.

Figure 3: Hardware/Software Parallel Development

In parallel *hardware/software* development, hardware and software teams work in lock-step, communicating regularly, and continuously integrating hardware and software. The simple way to think about this trend is that important tasks that were done later in the design flow are now being started earlier. The software development begins before hardware is completed by using hardware simulation models of electrical and electronic components replacing their physical counterparts. Prime examples of hardware/software parallel development are the efforts in software development that are early enough to contemplate hardware changes, i.e., for e.g., hardware optimization and hardware dependent software optimization.

The motion control systems shown before have to cope with failures of all kinds to guarantee safety of operators and machine integrity at any time. Validation of this ability

today is still mostly done by final integration and system tests on hardware after development. These tests are already complex and expensive today and are not able to completely cover all possible kinds of failures, as certain failures cannot be provoked in real hardware. Moreover, the late execution of the tests may cause long iteration loops in case weaknesses are detected in final tests. Early and comprehensive statements about system behaviour under fault conditions are necessary and should be integrated into the product development, a way to counter these pressing problems.

ESL (Electronic System Level) design and verification [5] is an established electronic design methodology at most of the world's leading SoC design companies and it is being used increasingly in system design. With ESL methodologies, the SoC designs are described and analysed at a level of abstraction at which the functional behaviour can be described without considering many details of the hardware implementation. Virtual prototyping is an ESL technique where a software simulation of the entire hardware platform is created using simulation models of the various blocks in the system [4]. A virtual prototype is a software functional model that implements the behaviour of the real hardware device and provides a lot of advantages. The models can be debugged and traced to capture all interface and internal hardware states and better controllability is supported which enables developers to modify hardware behaviour's for software and system validation. However, virtual prototyping works well for software development but falls short when more detailed hardware models are required and it is plagued by model availability, its creation cost and effort. VPs also suffer from less tool support and methodology features e.g., VPs lack simulator support with inherent fault-injection features which considerably hinders the development and validation of complex industrial electronic systems.

Due to the heterogeneous nature of system components in industrial electronic systems, full-system simulation is necessary since the isolated view of individual subsystems comprising a closed-loop control system does not suffice to represent and thus validate the overall functionality. As strong interdependencies between subsystems exist, the interactions between them are of importance [6], which highlights the need for multi-domain simulation. Multi-domain simulation is the ability to efficiently and accurately simulate systems by consideration of different domains (e.g., thermal, electrical, mechanical, hardware/software,

etc.) together within one simulation or a coupled co-simulation [7]. Therefore, fast and accurate time-domain simulations are crucial in today's heterogeneous systems simulation, design exploration, and verification. Hence, the full-system simulation at higher levels is performed provided it enables realistic system design and testing. Designers currently use high-level system design languages, such as SystemC, to model only the digital parts of a system. Simulink [8] and SystemC-AMS [9] are two well-known modeling languages used to model non-digital components of a system and its building blocks behaviourally.

#### 1.1 Research Contributions

In this work, we propose a virtual stress test methodology [10] based on fault injection into multi-domain virtual platforms to ease and speedup system validation against failures. Multi-Domain Virtual prototypes (MDVPs) [11] can be used for early validation by performing fault effect simulation abstracting the hardware components which the software is developed for. This allows the control software to protect against a wide variety of errors through extensive stress tests and also protection even against errors that up to now could not or barely been tested with real hardware setups. Thus, the security of systems is additionally increased despite its rapidly growing complexity.

A common methodology to perform efficient fault effect simulation of heterogeneous system parts are necessary to successfully validate and also to provide comprehensive statements about system behaviour in presence of faults. We define techniques to model faults across different domains, which can be used to conduct fault injection simulations in multidomain virtual prototypes. These techniques are used to enhance the physical component models before integrating them into the virtual platform. Non-digital parts of the system are often modeled in industry using MATLAB/Simulink. For the digital parts of the system we use transaction-level modeling (TLM) -based fault injection techniques [12] by defining appropriate fault models. But fault simulations in such systems can only be done based on virtual prototypes at high abstraction levels, which allow for execution of real SW stacks within only minutes of simulation time. At high abstraction level, it is difficult to validate fault injection as these models are not accurate enough to simulate the physical behaviour.

The key to capturing physical system behaviour in presence of faults is to have an accurate and appropriate multi-domain simulation model of a physical system, which incorporates important mechanisms such as electrical effects, magnetic effects, mechanical loading etc. Modeling these mechanisms is difficult and more importantly simulating such a system is very slow. We propose to go from an accurate simulation model to allow for consideration of the true physical effects to the abstract representation which is fast and detailed enough to simulate the behaviour of the overall system. Once we have both the accurate and the abstract simulation models, the effect of a particular fault can be transferred by following these steps. (i) Simulate the accurate model in presence of the fault and capture the behaviour (ii) Transfer the fault behaviour onto the abstract model and simulate the overall system. We also propose and develop a generic fault injection framework based on virtual prototypes for fault effect simulation of industrial motion control systems. Once the models are integrated into a virtual platform, the automated stress tests are carried out using scripts or each individual test interactively.

#### 1.2 Thesis Outline

Chapter 2 provides background knowledge for the remainder of this thesis. It starts by explaining the ESL methodology and system level design along with virtual porotypes. After that, we discuss the modeling of digital and analog/mixed-signal parts of the industrial systems in detail. Later, we will look at the model-based design and in-the-loop technologies. Finally, we briefly discuss the functional safety standards IEC61508 and ISO26262.

Chapter 3 describes the state-of-the-art relevant for work presented in this thesis. It also describes the motion control systems (MCS) along with providing exemplary faults in heterogeneous component parts in MCS. Later, fault injection current techniques are discussed. At the end, details of the research context which includes aim and research objectives along with methodology are given.

Chapter 4 describes the proposed concept for successfully conducting stress tests based on virtual prototyping. This chapter defines modeling techniques for analog and analog/mixed signal models to incorporate fault models for using inside virtual prototypes. Abstract fault models for analog and analog/mixed signal and also digital parts based on TLM

are defined. A concept to transfer fault behaviours from electrical to data-flow models is proposed and presented with examples. A generic fault injection framework to carry out fault injection tests using automated scripts with post processing is described.

Chapter 5 presents the implementation details of an industrial motor control application and automated fault injection tests along with results.

Chapter 6 presents the demonstrators for industrial use cases. These include two virtual HIL; condition monitoring of motor using an acceleration sensor and a conveyor belt application using a virtual robotic experimentation platform (V-REP simulator). Finally, HIL demonstrator based on SINAMICS G120 drive with fault injection is presented.

Chapter 7 presents the conclusions on what has been achieved in this work and proposes future prospects.

# 2 Background

## 2.1 Electronic System Level (ESL)

ESL (Electronic System Level) design and verification [5] is an established electronic design methodology at most of the world's leading SoC design companies and it is being used increasingly in system design. With ESL methodologies the SoC designs are described and analysed at a level of abstraction at which the functional behaviour can be described without many details of the hardware (RTL) implementations. Hence many engineering tasks and design optimizations can be sufficiently accomplished more quickly, efficiently and cheaply than at the RTL.

#### 2.1.1 ESL Design Methodology

The "design gap" shows the spread between technology capabilities and hardware design capabilities. The rising "design gap" demands for continuous improvements of the design productivity. One of the most critical issues is how the available chip has to develop even more complex integrated circuits and systems under fixed time-to-market and quality constraints. Here, designers describe an integrated circuit with an HDL (e.g. Verilog or VHDL) at RTL. There, the design is (almost) automatically synthesized down and circuit tool suites are applied using techniques such as tracking and reporting information about the code coverage, or performing a constraint random simulation. Two basic approaches could help to improve the design productivity: The first one lifts the design level to a higher more abstract level above RTL. The second approach introduces a design reuse methodology by means of (third-party) IP components. Modern flows combine both approaches to maximize benefits.

The SystemC TLM standard [13] does not focus on abstraction levels. In fact, the standard mentions particular use cases, such as software development, software performance analysis, or hardware architecture analysis. These use cases are supported by two different

coding styles, i.e. loosely-timed and approximately-timed modeling. Coding styles guide the designer in model writing using particular programming interfaces.

#### 2.1.2 System Level Design using SystemC

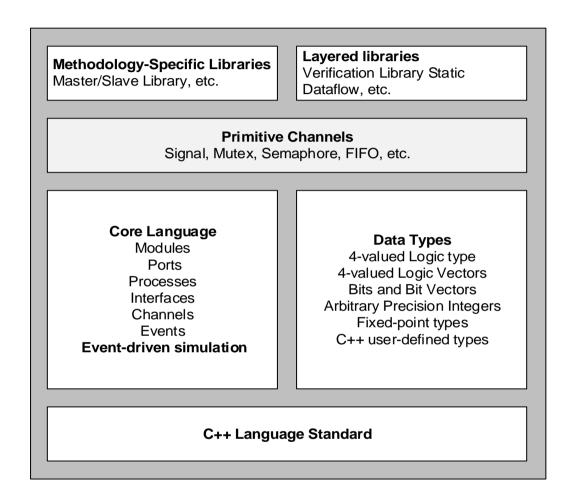

Figure 4: SystemC language architecture [14]

SystemC is the most accepted system level modeling language for system on chip design in the Electronic Design Automation (EDA) community. SystemC was introduced in 1999 by the Open SystemC Initiative (OSCI), which in 2011 merged with the Accellera Systems Initiative [15]. SystemC is an ANSI (American National Standards Institute) standard C++ class library [14] that allows modeling and dynamic verification of system level designs in various modeling abstractions. This includes classical RTL hardware modeling up

to transaction-level design. SystemC together with standard C++ software development tools are used to create system-level behavioural and architectural models of embedded systems. They provide hardware and software development teams a virtual platform for design, verification and test purposes without the need of hardware prototypes.

SystemC is both a system level design language and an even-driven simulation kernel. Figure 4 shows the layers of the SystemC library. The base layer highlights the fact that SystemC is built on top of C++, which makes it compatible with standard compilers and software development tools. The SystemC standard defines the three middle blocks. It defines the simulation kernel and the core language which together provide the main mechanisms for HW/SW co-design.

SystemC also defines the data types and elementary channels supporting libraries. The data type library is used for hardware modeling and for certain kinds of software programming, such as bits and bit vector data types for hardware and fixed-point data types for software implementations. Elementary channels include basic communication models widely applicable for hardware and software modeling. Finally, the upper blocks are examples of MoC and methodologies supported by SystemC, but are not included as part of the standard. They provide additional support for specific design methodologies and can be extended or form part of other standards. Further information regarding SystemC can be found in [16] and [17].

#### 2.1.3 Virtual Prototypes

A virtual prototype [4] is an executable software model of a hardware/software system that runs on a host computer. These are system level simulation models that emulate (mimic) the behaviour of hardware prototypes and execute unmodified production code and provide higher debugging and analysis efficiency. Virtual prototypes are composed of system level models of processing elements and peripherals, such as memories, buses, interrupt controllers, etc. Their early availability, binary software compatibility and high execution performance enable virtual prototypes to be used to develop, debug, integrate and validate system software long before the first set of physical development targets becomes available and in most cases, even before the chip hardware design is done.

A virtual platform is a fully functional software representation of a hardware design that encompasses a single- or multi-core SoC, peripheral devices, I/O and even the user interface. The virtual platform runs on a general-purpose PC or workstation and is detailed enough to execute unmodified production code including drivers, the OS and applications at reasonable simulation speed. Users have articulated the need for virtual platforms to not be slower than 1 tenth of real time to be effective for embedded software development. The achievable simulation speed depends on the level of model abstraction, which also determines the platform's accuracy.

Virtual platforms can be used in most stages of a design. The main applications of virtual prototypes are during the development phase. They are especially useful in the following cases: software-driven verification and software development. Software-driven verification is equivalent to software-in-the-loop testing, where production code can be verified inside a virtual platform along with a simulated environment. This facilitates the verification process without the need of real hardware prototypes and experimental setups. In early design stages, virtual platforms are used as executable specification models that capture HW and SW requirements at a high abstraction. Due to their high abstraction, they can be made available in less time and can serve as golden reference models for further development and refinement stages.

Virtual platforms are also very useful for software development. Initial software applications and drivers can be developed and tested using virtual platforms. This allows the identification of software bugs and communication bottlenecks, which might be too complicated to find in real prototypes. Virtual platforms can also be useful after the deployment of a product. For instance, they may be used by a software designer to verify software updates in the form of firmware or higher level functionalities, done on multiple versions of deployed products which may not be physically available at the moment of testing the update. Aside from the previously stated verification benefits, virtual prototypes enable many other testing capabilities such as performance optimization, power analysis and fault injection.

#### 2.1.3.1 Processor Models

Processor models use instruction set simulators (ISS) [18] to emulate the behaviour of the implementation model. By being an abstract representation of the RTL model, the simulation performance gained is typically several orders of magnitude faster than the implementation model. This allows hardware and software designers to run more application code or more comprehensive verification suites to prove the design. Processor models are system level descriptions of processing elements, such as microcontrollers, DSP's used in embedded systems. They are responsible for the simulation of binary code compiled for particular processor architectures and for their communication with other components inside a virtual platform. The processor models are composed of structural and behavioural descriptions. Structural descriptions contain architectural details of a processor such as functional units, caches, registers, counters, etc. Behavioural descriptions correspond to a software application that is loaded into the system model. Timing information is afterwards obtained by the combined interaction of structural and behavioural descriptions. The behaviour and timing information of a processor model is dictated by an Instruction Set Simulator (ISS). An ISS is used to perform binary translation of a software application complied for a specific microprocessor or DSP [19] instruction set and to execute it in a host computer.

Synopsys [4] virtual platforms provide comprehensive models of physical platforms. Virtual platforms combine high-speed processor instruction-set simulators and fully functional C/C++ transaction-level models (TLM) of the hardware building blocks to provide a high-level model of the hardware for early software development. The functionally accurate ARM Instruction Set Models are available from Synopsys which are fully validated against ARM processor designs and include modeling of advanced ARM technologies such as TrustZone and VFP (Vector Floating Point) [20]. Fast Models [21] uses Code Translation (CT) processor models, which translate ARM instructions into the instruction set of the host dynamically, and cache translated blocks of code. This and other optimization techniques, for instance temporal decoupling and Direct Memory Interface (DMI), produce fast simulation speeds for generated platforms, between 20-200 MIPS on a typical workstation enabling an

OS to boot in tens of seconds. They allow full control over the simulation, including profiling, debugging and tracing.

## 2.2 Digital Component Modeling

#### 2.2.1 Introduction

The growing complexity in modern SoC (System on Chip) [22] is forcing the industry to look for design methodologies above RTL that can be used for architectural analysis and embedded software development. In system level design of these SoCs, communication takes the central role. Therefore a methodology for modeling communication at a higher abstraction level has become important. TLM is one such methodology that promises to be used in system level SoC modeling for early software development, architectural analysis and functional verification [23].

#### 2.2.2 Transaction Level Modeling (TLM)

TLM is a transaction based modeling approach founded on high-level modeling languages such as SystemC. It highlights the concept of separating communication from computation within a system. TLM aims at enabling system level simulation of large systems, for which RTL simulation would require an unacceptable amount of time. This goal is achieved by abstracting from signal level communication and modeling complex communication operations as atomic transactions, thereby reducing the number of events to be processed by event-driven simulators.

TLM defines a transaction as a data transfer or synchronization between two modules at an instant. The definition of transaction is refined as a structure that is specific to bus protocol. The application of TLM is not tied with one programming language.

#### 2.2.2.1 Overview of TLM2.0 Standard

TLM enables simulation of complete hardware-software systems at much higher speeds. The simulation of TLM model is often orders of magnitude faster compared to RTL and low level

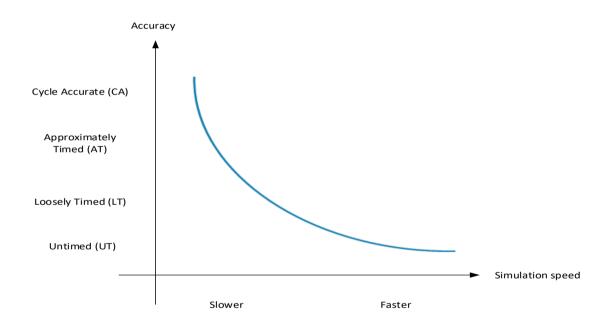

models. TLM models are used for different purposes by different people. Abstraction level of the model and their accuracy depends on use case and it is the clear trade-off between simulation speed and accuracy as shown in Figure 5.

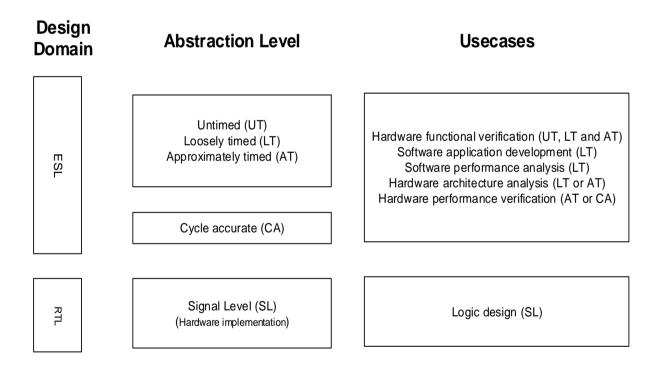

Virtual platform created using TLM at different abstraction levels can be used for different purposes (see Figure 6).

- For architectural exploration and performance analysis, especially of large systems, where the efficiency of the high-level TLM model enables rapid simulation.

- As a platform for early application software development, since the TLM definition of the hardware functionality can have enough detail for software to run on it and be available months before a detailed RTL implementation.

Figure 5: Simulation speed versus accuracy trade-off [13]

As a golden reference model for hardware verification, since TLM wrappers can be used to create a consistent interface to functional blocks whose detailed implementation is evolving.

The precision or correctness of a model in replicating the intended behaviour and activities of a system-under-design is determined by modeling accuracy of a given modeling approach. There are two decisive factors which determine the accuracy of a model, communication data granularity and timing accuracy.

The precision or correctness of a model in replicating the intended behaviour and activities of a system-under-design is determined by modeling accuracy of a given modeling approach. There are two decisive factors which determine the accuracy of a model, communication data granularity and timing accuracy.

• Communication data granularity: This criterion reflects the fineness of the data carried by the communication structure of a model. In the order of increasing accurateness, the data granularity can be broadly categorized into application packet, bus packet, and bus size levels.

Figure 6: Use cases and abstraction levels [13]

• Timing accuracy: Timing accuracy of a TLM model determines the fidelity of the model to the intended timing behaviour. Based on the timing accuracy, TLM models can be broadly classified into timed and untimed models. These models are tailored for different purposes. Untimed TLM model is an architectural model targeted specifically at early functional software development and functional verification where timing annotations are not necessary. The objective of this model is high simulation speed. On the other hand, timed model is less abstract and it focuses on simulation accuracy. It can be conceptually perceived as a scale of two extremes, i.e. untimed model and CA (Cycle Accurate) model. The timing accuracy of TLM model is increased as we move from untimed to CA level end as shown in Figure 6.

Although the AT coding style enables the creation of more accurate models than the LT coding style, the amount of communication timing details that can be modeled is still limited as it uses only four transaction phases. For SoC design use cases such as detailed performance analysis and hardware/software validation that require even more accuracy, the base protocol of the AT coding style is insufficient. Typically these use cases require the communication to be accurate at the level of the system clock. At this cycle-accurate (CA) level of abstraction, the approximately-timed base protocol must be replaced with a more specific communication protocol [24]. For specific communication protocols that require additional timing points, the base protocol can be extended with custom phases.

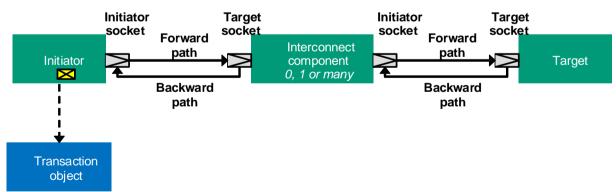

Figure 7: TLM-2.0 communication [13]

The SystemC TLM2 standard distinguishes between coding styles and interfaces instead of defining abstraction levels for each particular use case. A use case can be for instance software development, software performance analysis or hardware verification. The coding styles guide the designer in system modeling where the interfaces define low-level programming mechanisms. The TLM2 standard defines two coding styles: loosely-timed and approximately-timed that is supported by particular blocking and non-blocking transport interfaces.

- A module can act in three different ways:

- Initiator: This module type creates new transactions and passes them to the channel by calling a predefined interface method.

- Target: A module of this type receives transactions and executes them according to the target module task.

- Interconnect: This component type forwards a transaction and possibly modifies it. So it acts as initiator and target at the same time.

The transportation path of a transaction that is going from an initiator to a target is also called the forward path. The opposite direction is named the backward path. Over the backward path, the target informs the initiator about the transportation state. Either the modified transaction object is returned or a specific backward method is called explicitly. Two socket types encapsulate the connection between components. The initiator socket enables interface calls on the forward path by a port and on the backward path by an export. The target socket offers the same mechanism in case of a backward path.

TLM-based methodology is increasingly used to improve the design productivity of complex systems. The communication interfaces enable TLM to achieve separation of communication from computation and interoperability between components. By incorporating TLM in a SoC design flow, it is possible to model systems at various abstraction levels.

# 2.3 Analog and Mixed-Signal (AMS) Modeling

#### 2.3.1 Introduction

Virtual prototyping is a well-known technique applied in digitally-oriented ESL design methodologies. The objective is to create a reference platform of the complete system or IC architecture (the "prototype" part) by an executable description captured as an abstract model (the "virtual" part), which is then simulated. In this way, virtual prototyping provides software developers and system architects an environment for software development, architecture exploration, or HW/SW co-design. However, virtual prototypes based on purely digital models and model descriptions may not offer an efficient way to capture analog behaviour, which is often an integral part of the embedded system. This can be a serious drawback, as the interfaces to the outside world which are analog in nature – are thus not adequately modeled or even not modeled at all. Examples of these analog interfaces are sensors and actuators or the power supply and management unit of an integrated circuit. Furthermore, for optimized system architectures containing analog, digital, and software functionality, the software or firmware often directly interacts with analog/mixed-signal (AMS) hardware. Therefore, the correctness and robustness of the system in terms of its architecture, functional aspects, and timing aspects cannot be validated in the analog or digital domain only hence mixed-signal simulations are needed.

## 2.3.2 Analog and Mixed-Signal Modeling Languages

VHDL-AMS, Verilog-AMS [25], and SystemC-AMS allow modeling of discrete and continuous-time signals or a combination of both. All the three afore said HDL languages can represent AMS systems at a higher level of abstraction by bringing down the simulation time while providing the intended functionality of the design. Simulink (Simscape) or other interpretation tools can be used to model AMS systems if supporting libraries and functions are available. Simulink has an in built analog tool set which can be used for AMS modeling and the accuracy results are comparable to that of spice simulation results. In the following section, we will briefly look at SystemC-AMS and Simulink (Simscape [26]).

#### **2.3.2.1 SystemC-AMS**

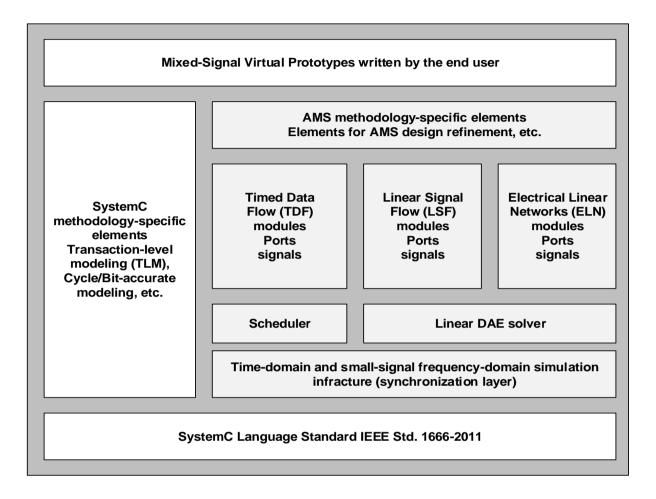

Figure 8: AMS Extensions for the SystemC Language Standard [9]

The SystemC-AMS language is an extension to the SystemC language. It enables analog and mixed-signal modeling and simulation capabilities. SystemC-AMS is not yet defined by an international standard, although a detailed documentation [9] and its respective proof-of-concept simulator [27] are available. SystemC-AMS extensions are fully compatible with the SystemC language standard as shown in Figure 8. The architecture of the SystemC-AMS language follows a layered approach built on top of the SystemC kernel. The user layer corresponds to the two top levels of Figure 8 and supports the following MoC's (Models of Computation): Electrical Linear Networks (ELN), Linear Signal Flow (LSF) and Timed Data Flow (TDF). The solver layer provides a linear DAE solver for ELN and LSF models and a scheduler for TDF models. The synchronization layer is responsible for embedding MoC

descriptions and their solvers/schedulers into data flow cluster processes [28] which are able to co-simulate with SystemC's discrete-event simulator.

The ELN MoC supports the modeling of non-causal continuous-time models described as electrical networks. Electrical network are built by the instantiation and interconnection of basic passive components derived from available macro models, such as resistors, capacitors and inductors, as well as sources and monitors. ELN does not support the use of non-linear elements (e.g. transistors and diodes), although there are some workarounds [29] [30]. A further limitation relies on the available linear DAE solver provided in the recent SystemC-AMS proof-of-concept simulator. The solver implements simple fixed-step numerical integration methods (a combination of backward Euler and trapezoid methods [31]) which may lead to numerical instabilities. The LSF MoC supports modeling of continuoustime systems described in a causal form using the following basic blocks: additions, multiplications, integration and delay. The connection of such blocks is used to define systems of equations, similarly to MATLAB /Simulink, which can be solved by the available linear DAE solver. The same limitations with respect to the linear DAE solver apply as before. The TDF MoC is an implementation of the Synchronous Data Flow (SDF) [32] principle, where processes are statically scheduled according to production and consumption rates. The advantage of TDF is the possibility to describe applications using a MoC similar to SDF. This is very useful for modeling digital signal processing algorithms. A further benefit is high simulation efficiency, since the TDF static scheduler reduces the dynamic overhead imposed by the discrete-event kernel of SystemC. SystemC-AMS is not yet a fully capable multi-domain simulator. It provides basic modeling capabilities for AMS systems in the electrical domain, but it lacks the modeling support for describing other type of physical energy domains. In addition, the available linear DAE solver in proof-of-concept simulator [27] is not robust enough, although improvements on this sense have been investigated [31].

#### 2.3.2.2 Simulink (Simscape)

Simulink is commercial software from Mathworks [8] for modeling, simulation and analysis of dynamic systems. It is a graphical programming environment used for creating models with block diagrams. It is capable of simulating models using different solvers and automatically

generating code. The basic elements in Simulink are blocks and lines. Basic blocks are mandatory units to perform computation or display functions, such as Add, Memory, Scope, etc. The designer builds hierarchical systems by encapsulating basic blocks into subsystems. Lines (also called edges or channels) are used to connect blocks and have register semantics (non-destructive read, destructive write). It has a large library of function blocks and users can also create their own customized blocks. By creating systems and subsystems in different blocks it is easy to organize a system and to get a clear overview of the different parts of the system, in a way that is often not available when using text based editors. Simulink provides several solvers to compute the model that contains continuous and/or discrete states. It is very efficient to use Simulink during early design stages for algorithm exploration. Simulink is often used in MBD (Model-Based Design). MBD is a process that enables fast and cost-effective development of dynamic systems, including control systems, signal processing, and communications systems.

Simscape [33] is one such toolbox which allows you to quickly create models of physical systems within the Simulink environment. With Simscape, you create physical component models based on physical connections that are directly integrated into block diagrams and other modeling paradigms. Simscape provides a set of block libraries and special simulation features especially for modeling physical systems that consists of real physical components. It is accessible as a library within the Simulink environment. They model systems such as electric motors, bridge rectifiers, hydraulic drives and cooling systems by combining essential components in a scheme. Simscape add-on products provide more complex components and analysis capabilities. From these different physical domains you can create models of your own custom components.

Simscape provides a foundation library with blocks from physical components for the domains mechanical, magnetic, electrical, hydraulic and thermal elements, as well as Simscape Multibody (formerly SimMechanics) for 3D mechanical systems, such as robots, vehicle suspensions, construction equipment, and aircraft landing gear. The following toolboxes are available, Simscape Driveline (formerly SimDriveline) for rotational and translational mechanical systems, Simscape Electronics (formerly SimElectronics) toolbox for electronic and mechatronic systems, Simscape Fluids (formerly SimHydraulics) for fluid

systems and Simscape Power Systems (formerly SimPowerSystems) for electrical power systems. To release designs to other simulation environments, consisting of HIL or vHIL systems, Simscape supports C-code generation. Transaction-Level Model Generation feature of HDL Verifier [34], when used with Simulink Coder automatically generates IEEE 1666 SystemC TLM 2.0 compatible transaction-level models. Generated SystemC models have a TLM 2.0 compliant interface with a target socket that uses the TLM 2.0 generic payload. You can select options for memory mapping, processing times as well as input and output buffering.

# 2.4 Model-Based Design and In-the-loop Technologies

Modeling is the step between the collection of high level requirements and implementation. Models allow testing and verification to be done continuously, in parallel with system design and implementation. In the early design stages, one can develop behavioural models to clarify and define detailed low level requirements. Such models may have the basic architecture of the solution, but are independent of the target platform. A model used to capture key requirements and to demonstrate correct behaviour in simulation, as well as to demonstrate traceability to high level requirements, is often referred to as executable specification. Further development of the executable specification and the addition of implementation details lead to the definition of a model that represents a final implementation. Often, such a model is optimized for code generation. It honours the data types, the target architecture and even the required coding style. Changes require a verification process that ensures the change introduced in the model for production code generation does not change the model's behaviour.

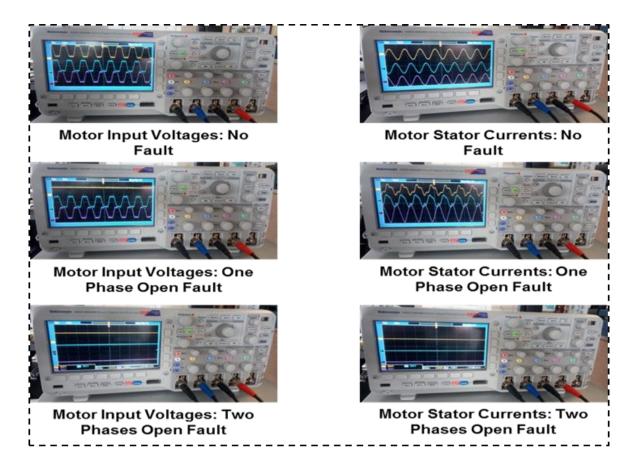

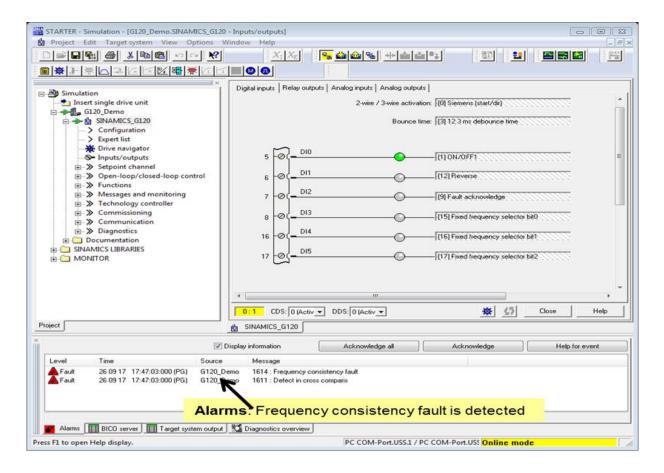

Figure 9: The V-model of the Systems Engineering Process